Difference between revisions of "KD11-D CPU"

(A pretty good start) |

m (clarify) |

||

| Line 5: | Line 5: | ||

Like other early, low-cost PDP-11s, it did not support either [[memory management]] of any kind, or hardware [[floating point]], [[PDP-11 Extended Instruction Set|EIS]] [[instruction]]s, or the various instructions added to the PDP-11 [[instruction set]] (XOR, SOB, SXT and MARK). | Like other early, low-cost PDP-11s, it did not support either [[memory management]] of any kind, or hardware [[floating point]], [[PDP-11 Extended Instruction Set|EIS]] [[instruction]]s, or the various instructions added to the PDP-11 [[instruction set]] (XOR, SOB, SXT and MARK). | ||

| − | There is a lack of clarity over the RTT instruction; some manuals say it is not | + | There is a lack of clarity over the RTT instruction; some manuals say it is not implemented, but the ''PDP-11 Architecture Handbook'' says "available in 11/04 but is different from other implementations". |

It was plugged into a modified [[Modified UNIBUS Device|MUD]] [[backplane]], either the the [[DD11-C backplane|DD11-C]] or [[DD11-D backplane]]s, or the special [[DD11-P backplane]] of the [[PDP-11/34]]. | It was plugged into a modified [[Modified UNIBUS Device|MUD]] [[backplane]], either the the [[DD11-C backplane|DD11-C]] or [[DD11-D backplane]]s, or the special [[DD11-P backplane]] of the [[PDP-11/34]]. | ||

| − | It supported the [[KY11-LA Operator's Console]] and the [[KY11-LB Programmer's Console]], including the maintainence functionality | + | It supported the [[KY11-LA Operator's Console]] and the [[KY11-LB Programmer's Console]], including the latter's maintainence functionality which allowed the CPU's microcode to be [[single-step]]ped. |

==KY11-LB Interface== | ==KY11-LB Interface== | ||

Revision as of 00:32, 19 January 2019

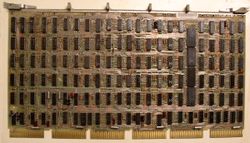

The KD11-D PDP-11 CPU of the PDP-11/04 was a micro-programmed processor contained on single hex card (the M7263), the first PDP-11 CPU to be built on a single card.

Like other early, low-cost PDP-11s, it did not support either memory management of any kind, or hardware floating point, EIS instructions, or the various instructions added to the PDP-11 instruction set (XOR, SOB, SXT and MARK).

There is a lack of clarity over the RTT instruction; some manuals say it is not implemented, but the PDP-11 Architecture Handbook says "available in 11/04 but is different from other implementations".

It was plugged into a modified MUD backplane, either the the DD11-C or DD11-D backplanes, or the special DD11-P backplane of the PDP-11/34.

It supported the KY11-LA Operator's Console and the KY11-LB Programmer's Console, including the latter's maintainence functionality which allowed the CPU's microcode to be single-stepped.

KY11-LB Interface

The microcode diagnostic interface to the KY11-LB is carried over a 10-wire flat cable connected to the J2 Berg connector header on the KY11-LB's M7859 module (the other 10-pin header on that card is unused with the -11/04), and a set of vertical pins in the upper left-hand corner (see image above) of the M7263. (The main functionality of the KY11-B is done over the UNIBUS, and a pair of backplane lines.)

| v • d • e PDP-11 Computers and Peripherals |

|---|

| UNIBUS PDP-11s - PDP-11/20 • PDP-11/15 • PDP-11/35 • PDP-11/40 • PDP-11/45 • PDP-11/50 • PDP-11/55 • PDP-11/70 PDP-11/05 • PDP-11/10 • PDP-11/04 • PDP-11/34 • PDP-11/60 • PDP-11/44 • PDP-11/24 • PDP-11/84 • PDP-11/94 QBUS PDP-11s - PDP-11/03 • PDP-11/23 • PDP-11/23+ • MicroPDP-11/73 • MicroPDP-11/53 • MicroPDP-11/83 • MicroPDP-11/93 QBUS CPUs: LSI-11 • LSI-11/2 • KDF11-A • KDF11-B • KDJ11-A • KDJ11-B • KDJ11-D • KDJ11-E Buses: UNIBUS • UNIBUS map • SPC • MUD • EUB • QBUS • CD interconnect • PMI Also: PDP-11 architecture • PDP-11 Extended Instruction Set • FP11 floating point • PDP-11 Memory Management |

| UNIBUS CPUs: KA11 • KC11 • KB11-A • KB11-B • KB11-C • KB11-D • KD11-A • KD11-B • KD11-D • KD11-E • KD11-EA • KD11-K • KD11-Z • KDF11-U

Co-processors: FP11-A • FP11-B • FP11-C • FP11-E • FP11-F • KE44-A • FPF11 Chips: LSI-11 • KEV11-A • KEV11-B • KEV11-C • F-11 • KEF11-A • KTF11-A • T-11 • J-11 • FPJ11 CPU options: KE11-E • KE11-F • KJ11-A • KT11-C • KT11-D • KK11-A • KK11-B • KT24 • KTJ11-B Rare CPU options: KS11 Memory Protection and Relocation option • KT11-B Paging Option • KUV11 Writeable Control Store Front panels: KY11-A • KY11-D • KY11-J • KY11-LA • KY11-LB • KY11-P More on buses: UNIBUS and QBUS termination • Bus Arbitration on the Unibus and QBUS • CTI BUS PDT-11s - PDT-11/110 • PDT-11/130 • PDT-11/150 CTI PDP-11s - PRO-325 • PRO-350 • PRO-380 Other: FIS floating point • PDP-11 Commercial Instruction Set • PDP-11 stacks • PDP-11 family differences |