Difference between revisions of "UDA50 Disk Controller"

m (Better cat) |

(UDA50 details) |

||

| Line 1: | Line 1: | ||

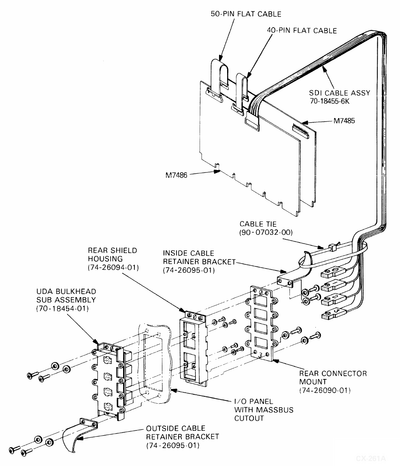

| − | + | [[File:UDA50 Field Replaceable Parts.png|400px|thumb|right|UDA50 Field Replaceable Parts]] | |

| − | + | The UDA50 is an intelligent controller which interfaces up to four [[Standard Disk Interconnect#SDI Family of DSA Products| SDI disks]] to any [[UNIBUS]] system. | |

| − | [[UNIBUS]] [[disk]] [[ | + | The UDA50 uses a radial bus configuration instead of the conventional daisy-chain (serial) method. |

| + | Radial configuration means there is a separate I/O cable going to each disk drive. | ||

| + | |||

| + | The UDA50 consists of two [[DEC card form factor|hex modules]] (8.5” by 15.6”) modules which can be mounted in a [[PDP-11]] or [[VAX]] UNIBUS [[backplane]] or expansion box, and associated mounting hardware and cables. | ||

| + | |||

| + | The modules are referred to as the microprocessor and SDI modules respectively, according to their principal functions, and communicate with each other by means of two ribbon cables. | ||

| + | Mounting hardware consists of locating brackets and bulkhead connectors for the shielded SDI cables leading from the disk drives to the UDA50's cabinet. | ||

| + | An unshielded intra-cabinet SDI cable is provided with the UDA50. | ||

| + | |||

| + | Dual microprocessors on one of the modules execute independent microprograms to maximize subsystem throughput. | ||

| + | Extensive buffering on the UDA50 modules matches host computer bus capacities to the requirements of high density disk drives. | ||

| + | Direct connection of the UDA50 to each drive maximizes subsystem availability. | ||

| + | Onboard diagnostic capability with fault reporting both to the host and through [[Light Emitting Diode|LEDs]] on the modules minimizes repair time. | ||

| + | |||

| + | == Microprocessor Module == | ||

| + | |||

| + | The UDA50 microprocessor module (M7485) contains two microsequencers which share an [[Arithmetic logic unit|arithmetic and logic unit (ALU)]]. | ||

| + | The two microprocessors execute independent micro programs from [[Read-only memory|read only memory (ROM)]] also located on the module. | ||

| + | One of the microprocessors, the UNIBUS microprocessor, handles transactions with the host computer and sets overall policy for UDA50 operation. | ||

| + | The other, the drive microprocessor, handles interaction with the disk drives including error recovery. | ||

| + | |||

| + | The microprocessor module performs all UDA50 interaction with the UNIBUS. It contains the two [[register]]s by which the UDA50 communicates with its host, and a switch pack for setting their addresses. | ||

| + | It also contains a mount for a standard UNIBUS interrupt priority plug. Host software defines the interrupt vector address during UDA50 initialization, so no hardware means of setting it is required. | ||

| + | |||

| + | The microprocessor module holds the standard UNIBUS data transfer chips, which perform cycle level transactions on the UNIBUS. | ||

| + | To avoid interference with UNIBUS devices having limited buffering, the module contains bus request delay jumpers, which maybe set to force a delay of 0, 6.2, or 10 microseconds between UDA50 UNIBUS accesses. | ||

| + | |||

| + | Finally, four LED indicators on the microprocessor module, together with four similar LEDs on the SDI module, report microdiagnostic detected failures, and indicate which part to replace. | ||

| + | |||

| + | == SDI Module == | ||

| + | |||

| + | The UDA50 SDI module (M7486) is the physical connection to the disk drives. It conducts data and control transactions through two ribbon cable busses running between it and the microprocessor module. | ||

| + | |||

| + | The SDI module contains terminators for the SDI cables which connect the UDA50 to its drives. | ||

| + | Since the SDI is a serial bus, parallel data in UDA50 buffer memory must be converted before being sent to a drive. | ||

| + | This is done by two custom [[Integrated circuit|LSI]] serialization/deserialization (SERDES) chips residing on the SDI module. | ||

| + | On a write, the SERDES chips serialize data for transfer to the drive. On a read, they perform the opposite function. | ||

| + | The SDI module includes switching logic for multiplexing the SERDES among the four drives that may be attached to the UDA50. | ||

| + | |||

| + | Also located on the SDI module is the buffer memory. | ||

| + | Consisting of 32 KBytes of static RAM with a word cycle time of 55 nanoseconds, the buffer memory is sufficient for 52 sector buffers (26 KBytes) plus a buffer for 20 host commands (plus one for immediate execution) and the data structures to manage both dynamically. | ||

| + | |||

| + | A major data integrity feature of SDI drives is the 170 bit Reed-Solomon [[Error-correcting code|ECC]]. | ||

| + | This ECC has a correction capability of up to 8 10-bit error bursts in a single sector compared to the single 11-bit burst capability of conventional codes. | ||

| + | Data passes through a custom LSI chip on its way to the drive, and the ECC is computed in real time. | ||

| + | At the end of each sector, the chip supplies the 170 bit ECC to be written with the data. | ||

| + | On a read operation, the ECC is both read and recomputed, and the chip supplies the miscompare pattern (if any). | ||

| + | If error correction is required, drive microprocessor microcode performs it. | ||

| + | |||

| + | == UDA50 Versions == | ||

| + | |||

| + | There are two versions of the UDA50: | ||

| + | |||

| + | * UDA50-00 (old version: M7161 & M7162) | ||

| + | * UDA50-A (upgraded version: M7485 & M7486) | ||

| − | |||

[[Category: UNIBUS Storage Controllers]] | [[Category: UNIBUS Storage Controllers]] | ||

Revision as of 09:46, 27 August 2022

The UDA50 is an intelligent controller which interfaces up to four SDI disks to any UNIBUS system.

The UDA50 uses a radial bus configuration instead of the conventional daisy-chain (serial) method. Radial configuration means there is a separate I/O cable going to each disk drive.

The UDA50 consists of two hex modules (8.5” by 15.6”) modules which can be mounted in a PDP-11 or VAX UNIBUS backplane or expansion box, and associated mounting hardware and cables.

The modules are referred to as the microprocessor and SDI modules respectively, according to their principal functions, and communicate with each other by means of two ribbon cables. Mounting hardware consists of locating brackets and bulkhead connectors for the shielded SDI cables leading from the disk drives to the UDA50's cabinet. An unshielded intra-cabinet SDI cable is provided with the UDA50.

Dual microprocessors on one of the modules execute independent microprograms to maximize subsystem throughput. Extensive buffering on the UDA50 modules matches host computer bus capacities to the requirements of high density disk drives. Direct connection of the UDA50 to each drive maximizes subsystem availability. Onboard diagnostic capability with fault reporting both to the host and through LEDs on the modules minimizes repair time.

Microprocessor Module

The UDA50 microprocessor module (M7485) contains two microsequencers which share an arithmetic and logic unit (ALU). The two microprocessors execute independent micro programs from read only memory (ROM) also located on the module. One of the microprocessors, the UNIBUS microprocessor, handles transactions with the host computer and sets overall policy for UDA50 operation. The other, the drive microprocessor, handles interaction with the disk drives including error recovery.

The microprocessor module performs all UDA50 interaction with the UNIBUS. It contains the two registers by which the UDA50 communicates with its host, and a switch pack for setting their addresses. It also contains a mount for a standard UNIBUS interrupt priority plug. Host software defines the interrupt vector address during UDA50 initialization, so no hardware means of setting it is required.

The microprocessor module holds the standard UNIBUS data transfer chips, which perform cycle level transactions on the UNIBUS. To avoid interference with UNIBUS devices having limited buffering, the module contains bus request delay jumpers, which maybe set to force a delay of 0, 6.2, or 10 microseconds between UDA50 UNIBUS accesses.

Finally, four LED indicators on the microprocessor module, together with four similar LEDs on the SDI module, report microdiagnostic detected failures, and indicate which part to replace.

SDI Module

The UDA50 SDI module (M7486) is the physical connection to the disk drives. It conducts data and control transactions through two ribbon cable busses running between it and the microprocessor module.

The SDI module contains terminators for the SDI cables which connect the UDA50 to its drives. Since the SDI is a serial bus, parallel data in UDA50 buffer memory must be converted before being sent to a drive. This is done by two custom LSI serialization/deserialization (SERDES) chips residing on the SDI module. On a write, the SERDES chips serialize data for transfer to the drive. On a read, they perform the opposite function. The SDI module includes switching logic for multiplexing the SERDES among the four drives that may be attached to the UDA50.

Also located on the SDI module is the buffer memory. Consisting of 32 KBytes of static RAM with a word cycle time of 55 nanoseconds, the buffer memory is sufficient for 52 sector buffers (26 KBytes) plus a buffer for 20 host commands (plus one for immediate execution) and the data structures to manage both dynamically.

A major data integrity feature of SDI drives is the 170 bit Reed-Solomon ECC. This ECC has a correction capability of up to 8 10-bit error bursts in a single sector compared to the single 11-bit burst capability of conventional codes. Data passes through a custom LSI chip on its way to the drive, and the ECC is computed in real time. At the end of each sector, the chip supplies the 170 bit ECC to be written with the data. On a read operation, the ECC is both read and recomputed, and the chip supplies the miscompare pattern (if any). If error correction is required, drive microprocessor microcode performs it.

UDA50 Versions

There are two versions of the UDA50:

- UDA50-00 (old version: M7161 & M7162)

- UDA50-A (upgraded version: M7485 & M7486)