KA650 Main Memory System

The KA650 Main Memory System is the main memory sub-system for the VAX KA650 CPU, and later KA655 CPU. It is split between the CPU card, which contains the main memory controller, and a number of MS650 boards; they communicate over the MS650 memory interconnect.

This page contains notes on troubleshooting, repair, and theory of operation of the KA650 Main Memory System.

Contents

Overview

The MS650-AA and MS650-BA memory modules were intended to be used with the KA650 CPU, as the name might suggest. These quad-width cards contain 8MB and 16MB of RAM for the VAX, respectively, complete with ECC.

Theory of Operation

Memory Controller General Architecture and Organization

Memory Control Signals Provided by the CMCTL

The CMCTL IC is the DRAM controller for the KA650 CPU. It has 10 address line outputs, 39 memory data I/O lines (MD), 4 CAS outputs, 4 RAS outputs, a WE pin, and an SE pin. Also available to the RAM card are the inverse of the 20th and 21st address lines (XA20 & XA21), which are used as bank selection when using 256kxX DRAM chips. The data lines are carried to the RAM cards through a 50 conductor ribbon cable, while the rest of the control lines are provided through the CD interconnect on the backplane. [1]

The 10 address lines carry the row address on the rising edge of a RAS line, followed by the column address on the rising edge of a CAS line.

The 39 data I/O lines carry the 32 data and 7 ECC bits for the RAM.

The 4 CAS (Column Address Strobe) lines allow strobing the column address on up to 4 separate memory modules.

The 4 RAS (Row Address Strobe) lines allow selection of up to 4 banks on a single memory module.

The WE (Write Enable) pin indicates that the CMCTL is writing to memory, rather than reading.

The SE (Strobe Enable?) pin seems to indicate that the CMCTL is refreshing memory. This is necessary for the 8MB card to correctly strobe the RAS lines of each bank during a refresh cycle, due to the extra RAS gating circuitry necessary on cards with 256kxX DRAMs.

The XA20 and XA21 lines are the inverse of the latched address lines from the CDAL bus.

Note that many of the above control lines are inverse logic from what is normally used to drive DRAMs; in particular, CAS, RAS, and WE lines are inverted from the normal JEDEC DRAM convention of active low /RAS, /CAS, and /WE.

Memory Ranks & Banks

Due to the 10 bit address bus using conventional multiplexed row and column DRAM addressing, an effective 20 bit address is formed. This allows the CMCTL to address up to 1MWord per rank.

By strobing different pairings of RAS and CAS (RAS0+CAS0 is one rank, while RAS0+CAS1 is another rank, while RAS1+CAS0 is yet another rank), the CMCTL supports up to 16 ranks of RAM, each 1Mx39. Each rank is thus 4MB of memory once ECC overhead is accounted for. This puts a 64MB cap on the maximum amount of memory the CMCTL can address (16 ranks of 4MB).

When 256kxX DRAMs are used in place of 1MxX DRAMs, each 1Mx39 rank is further divided into 4 banks of 256kx39. Each bank is selected by XA20 and XA21, which are provided to the RAM cards via the CD interconnect. These address bits appear to only be valid on the rising edge of RAS. Before CAS has strobed, the bits have generally already changed since these are derived from the CDAL bus of the VAX CPU. These bits are used to gate the /RAS lines to the DRAMs ensuring that only the selected bank is addressed. The /CAS line for the card is not affected.

The MS650-AA card contains 312 256kx1 ZIP DRAMs, organized into 8 banks of 256kx39. As previously mentioned, one memory rank as addressed by the CMCTL memory controller consists of 4 banks, making up a total of 1MWord of memory per rank. Each DRAM on the card corresponds to one bit of the 39 bit word within a 1MB address region of the VAX.

Addressing

The CMCTL appears to convert 32 bit VAX addresses into DRAM addressing as follows:

| A21 | A20 | A19 | A18 | A17 | A16 | A15 | A14 | A13 | A12 | A11 | A10 | A09 | A08 | A07 | A06 | A05 | A04 | A03 | A02 |

| R09 | R08 | R07 | R06 | R05 | R04 | R03 | R02 | R01 | R00 | ||||||||||

| C09 | C08 | C07 | C06 | C05 | C04 | C03 | C02 | C01 | C00 |

Axx are VAX address lines Rxx are DRAM row address bits Cxx are DRAM column address bits

This addressing scheme is used to ensure that 256kxX DRAMs (which use only 9 bit row and column addresses) are still supported for use with the CMCTL.

It is, of course, still up to the CMCTL to determine which ranks are selected by the upper bits of a given physical address. This is determined by the MEMCSR0-15 registers, which seem to specify whether or not a bank is present, as well as what base address it resides at. It may perform other functions, but it does not seem to be documented in available documentation.

CAS and RAS Signals

Each 16MB or 8MB memory card for the KA650 uses one CAS line in its entirety. This is why a maximum of 4 cards may be used in a KA650 system. Each RAM card uses the first CAS line, and passes the remaining lines on to the next card, shifted down one bit. So for example, the first card gets CAS0 CAS1 CAS2 CAS3, in that order. It uses CAS0 and passes CAS1 CAS2 and CAS3 on to the next card, in that order. The next card uses CAS1 and passes on CAS2 and CAS3. This repeats until 4 cards have used up all of the available CAS lines.

The CAS line is not gated in any way on the MS650-AA. The CAS line is simply buffered, inverted to match the polarity of the DRAMs, and distributed to all DRAMs on the card (likely with some hierarchical buffering methodology).

RAS lines, on the other hand, are shared between all the cards in the system. The first rank of DRAMs on the card are address by RAS0, the second by RAS1, etc. As previously mentioned, the RAS lines to each bank within a rank are gated on or off by decoding circuitry based on the state of XA20/XA21.

Refresh

DRAMs are built using one tiny MOS capacitor for each bit. These capacitors leak slightly and need to be periodically refreshed. DRAM rows are refreshed by simply addressing a row. Any row access refreshes that row, no column needs to be strobed for a refresh.

As such, during refresh cycles, the CMCTL places a row address to be refreshed on the address bus, asserts SE, and asserts all RAS lines for several clock cycles. The purpose of the SE signal is so that RAM cards with 256kxX DRAMs do not gate any of the /RAS lines going to the DRAMs, or else only whatever DRAM bank is (randomly) addressed by XA20 and XA21 would be refreshed.

ECC

The ECC supported by the CMCTL has the ability to detect and correct single data bit errors, detect single ECC bit errors, and detect double-bit data errors. [2]

ECC is generally based on producing parity bits of various collections of data bits. Since parity is based around the simple XOR, it is a linear operation in a manner of speaking. Luckily this means we can determine the ECC equations based on a number of sample data patterns and the respective ECC bits, such as the ECC produced for 0 data, and data with only one bit in the word set. By comparing the ECC for each test pattern to that of 0, we can determine which ECC bits each bit in the data word affects.

| bit | data | ECC | |||||||

| MSB | LSB | ||||||||

| - | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0111100 |

| 0 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0001 | 1100100 |

| 1 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0010 | 0100000 |

| 2 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0100 | 0100110 |

| 3 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 1000 | 1100010 |

| 4 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0001 | 0000 | 0100011 |

| 5 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0010 | 0000 | 1100111 |

| 6 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0100 | 0000 | 1100001 |

| 7 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 1000 | 0000 | 0100101 |

| 8 | 0000 | 0000 | 0000 | 0000 | 0000 | 0001 | 0000 | 0000 | 1010100 |

| 9 | 0000 | 0000 | 0000 | 0000 | 0000 | 0010 | 0000 | 0000 | 0010000 |

| 10 | 0000 | 0000 | 0000 | 0000 | 0000 | 0100 | 0000 | 0000 | 0010110 |

| 11 | 0000 | 0000 | 0000 | 0000 | 0000 | 1000 | 0000 | 0000 | 1010010 |

| 12 | 0000 | 0000 | 0000 | 0000 | 0001 | 0000 | 0000 | 0000 | 0010011 |

| 13 | 0000 | 0000 | 0000 | 0000 | 0010 | 0000 | 0000 | 0000 | 1010111 |

| 14 | 0000 | 0000 | 0000 | 0000 | 0100 | 0000 | 0000 | 0000 | 1010001 |

| 15 | 0000 | 0000 | 0000 | 0000 | 1000 | 0000 | 0000 | 0000 | 0010101 |

| 16 | 0000 | 0000 | 0000 | 0001 | 0000 | 0000 | 0000 | 0000 | 1001100 |

| 17 | 0000 | 0000 | 0000 | 0010 | 0000 | 0000 | 0000 | 0000 | 0001000 |

| 18 | 0000 | 0000 | 0000 | 0100 | 0000 | 0000 | 0000 | 0000 | 0001110 |

| 19 | 0000 | 0000 | 0000 | 1000 | 0000 | 0000 | 0000 | 0000 | 1001010 |

| 20 | 0000 | 0000 | 0001 | 0000 | 0000 | 0000 | 0000 | 0000 | 0001011 |

| 21 | 0000 | 0000 | 0010 | 0000 | 0000 | 0000 | 0000 | 0000 | 1001111 |

| 22 | 0000 | 0000 | 0100 | 0000 | 0000 | 0000 | 0000 | 0000 | 1001001 |

| 23 | 0000 | 0000 | 1000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0001101 |

| 24 | 0000 | 0001 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000100 |

| 25 | 0000 | 0010 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 1000000 |

| 26 | 0000 | 0100 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 1000110 |

| 27 | 0000 | 1000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000010 |

| 28 | 0001 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 1000011 |

| 29 | 0010 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000111 |

| 30 | 0100 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000001 |

| 31 | 1000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 1000101 |

The results of this are depicted below. The basic result is that toggling one of the bits that belongs to the ECC bit group will result in that ECC bit toggling as well.

| ECC bit | MSB | LSB | ||||||||||||||||||||||||||||||

| MD32 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | ||||||||||||||||

| MD33 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | ||||||||||||||||

| MD34 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | ||||||||||||||||

| MD35 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | ||||||||

| MD36 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | ||||||||

| MD37 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | ||||||||

| MD38 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | ||||||||||||||||

An interesting and potentially useful point to note is that flipping bit 28 happens to flip all of the ECC bits together. Another interesting point is that inverting the entire data word produces the same ECC.

From this information, we can derive some data patterns that produce useful ECC combinations, such as ECC of all zeroes, all ones, only one bit set, and only one bit clear. Looking at the table above, we got lucky and examples of many of these combinations were found by chance. In particular, we happened upon data combinations that produced every possibility of 1 ECC bit set. These, combined with the fact that we can toggle bit 28 to get the inverse ECC bits, gives us a set of data patterns which produce ECC with only one bit clear. From here, we only need to derive a combination which produces all-zero ECC, and from that, derive all-one ECC.

Starting with the ECC for bit 31 set, we can toggle single bits at a time until we find a combination that produces the ECC we want.

31 1000 0000 0000 0000 0000 0000 0000 0000 1000101

1000 0000 0000 0000 0000 0000 0000 0001 0011101

1000 0000 0000 0000 0000 0010 0000 0001 0110001

1000 0000 1000 0000 0000 0010 0000 0001 0000000 <--

1001 0000 1000 0000 0000 0010 0000 0001 1111111 <--

The summary of these useful ECC combinations is tabulated below (data in hex, ECC in binary)

useful ECC combinations:

| ECC (binary) | data (hex) |

| 0000000 | 80800201 |

| 0000001 | 40000000 |

| 0000010 | 08000000 |

| 0000100 | 01000000 |

| 0001000 | 00020000 |

| 0010000 | 00000200 |

| 0100000 | 00000002 |

| 1000000 | 02000000 |

| 1111111 | 90800201 |

| 1111110 | 50000000 |

| 1111101 | 18000000 |

| 1111011 | 11000000 |

| 1110111 | 10020000 |

| 1101111 | 10000200 |

| 1011111 | 10000002 |

| 0111111 | 12000000 |

KA650 Memory Bus Cycles

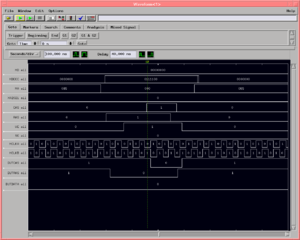

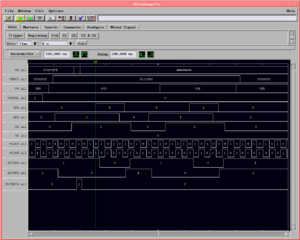

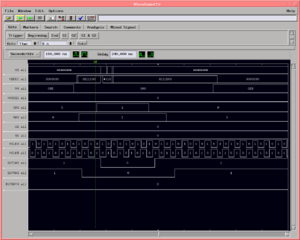

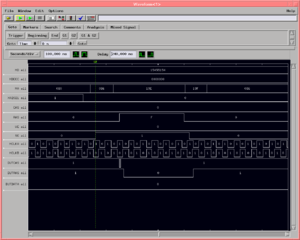

The memory cycles detailed below were captured on an HP 16700A logic analysis system. Memory data and ECC bits were captured, as well as memory address, XA20 and XA21 (inverted back to positive logic by the logic analyzer), the 4 CAS lines, the 4 RAS lines, the WE line, the SE line, the MCLK lines for timing reference. Additionally, the /CAS (DUTCAS), /RAS (DUTRAS), and data line (DUTDATA) of a DRAM located at 0x0XXXXX, bit 0 were captured to show the differences between a selected DRAM and one that was not selected.

During a longword write cycle, the CMCTL first places the row address onto the memory address bus. Next, it asserts the RAS signal, causing the DRAMs to latch the row address. It then asserts the write enable signal and places the column address on the address bus, then asserts the CAS signal. Lastly, the data and ECC bits are placed on the bus, and some time later CAS deasserts, followed by RAS. On the MS650-AA RAM module, XA20 and XA21 are decoded to determine which bank is selected. Since the DUT being probed here is at address 0x0XXXXX, it is selected during this write.

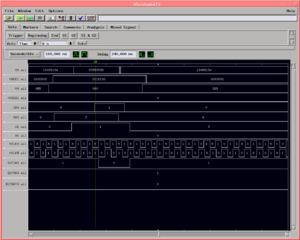

The CMCTL will assert only the RAS line for the rank which is selected based on the memory address the VAX CPU is accessing. As shown in the next capture, when an address in 0x1XXXXX is written, RAS2 is asserted instead, and thus the DUT being probed was not selected.

Likewise, the MS650-AA decoding circuitry will only allow the RAS line for the bank selected by XA20 and XA21 to be asserted, while ensuring the RAS lines for the other banks are gated off.

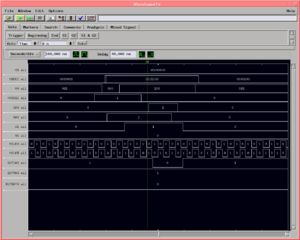

During a byte write cycle, the CMCTL must first read the entire 39 bit word from the MS650, modify the byte which is being written, recalculate the ECC bits, and write the entire 39 bit word back to the MS650. Due to this, both a read and write cycle can be seen within a byte write cycle. Note that the RAS line stays asserted throughout both the read and write parts of the cycle.

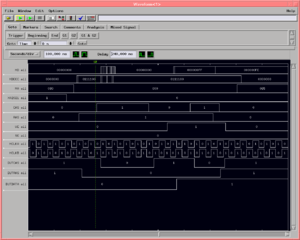

During a quadword write cycle, two 39 bit words must be written to the MS650. Note that RAS actually cycles twice during this cycle.

Any read cycle longword or smaller will appear to have the same cycle. Since the MS650 must be read or written as a full 39 bit cycle, there is no effective difference between a byte, word, or longword read. A quadword read, of course, involves reading two 39 bit words, and would thus result in a double cycle similar to the quadword write.

Lastly, during a refresh cycle, the SE signal is asserted to force an MS650-AA to allow all banks to be refreshed at once. This would not be necessary for the 1MxX DRAMs on an MS650-BA. Similarly, the CMCTL asserts all RAS lines to load the row to be refreshed into every DRAM connected to the KA650. There is no assertion of CAS since there is no need to actually access a specific location, just to refresh a given row.

Memory Connector Pinouts

The MS650 boards and KA650 CPU board communicate through the CD interconnect and a 50 pin ribbon cable. The pinouts are available and can be deduced from the KA650 technical manual and field maintenance print set. They are repeated here for ease of use.

Although the memory card is in a Q-bus form factor, and it has edge connectors for the Q-bus half of the backplane (AB connectors), it does not seem to use any q-bus signals for operation other than power supply pins.

Data Bus Connector

| pin | signal | pin | signal |

| 01 | GND | 26 | D MD10 H |

| 02 | D MD9 H | 27 | GND |

| 03 | D MD8 H | 28 | D MD29 H |

| 04 | D MD7 H | 29 | D MD28 H |

| 05 | GND | 30 | D MD27 H |

| 06 | D MD6 H | 31 | GND |

| 07 | D MD5 H | 32 | D MD26 H |

| 08 | D MD4 H | 33 | D MD25 H |

| 09 | D MD3 H | 34 | D MD24 H |

| 10 | GND | 35 | D MD23 H |

| 11 | D MD2 H | 36 | GND |

| 12 | D MD1 H | 37 | D MD22 H |

| 13 | D MD0 H | 38 | D MD21 H |

| 14 | D MD19 H | 39 | D MD20 H |

| 15 | GND | 40 | D MD38 H |

| 16 | D MD18 H | 41 | GND |

| 17 | D MD17 H | 42 | D MD37 H |

| 18 | D MD16 H | 43 | D MD36 H |

| 19 | D MD15 H | 44 | D MD35 H |

| 20 | GND | 45 | D MD34 H |

| 21 | D MD14 H | 46 | GND |

| 22 | D MD13 H | 47 | D MD33 H |

| 23 | D MD12 H | 48 | D MD32 H |

| 24 | GND | 49 | D MD31 H |

| 25 | D MD11 H | 50 | D MD30 H |

CD interconnect

Note that DEC pin naming conventions follow the DEC alphabet, skipping various letters which could be mistaken for numerals.

| signal | pin |

| MA0 | DB2 |

| MA1 | DE2 |

| MA2 | DH2 |

| MA3 | DJ2 |

| MA4 | DL2 |

| MA5 | DM2 |

| MA6 | DP2 |

| MA7 | DR2 |

| MA8 | DS2 |

| MA9 | DU2 |

| XA20 | CV2 |

| XA21 | CU2 |

| CAS0 | CF2 |

| CAS1 | CK2 |

| CAS2 | CN2 |

| CAS3 | CS2 |

| RAS0 | CE2 |

| RAS1 | CJ2 |

| RAS2 | CM2 |

| RAS3 | CR2 |

| WE | CB2 |

| SE | CA1 |

KA650 VAX Firmware Memory Tests

Many of the tests built in to the firmware of the VAX can be quite thorough, if used properly. The tests can be accessed by the TEST command in the monitor, abbreviated to 't'.

The tests report diagnostic information upon failure, encoded simply as a number of values in registers and memory locations on the stack. With the proper documentation, these values could be decoded to determine the problem. Lacking that documentation, I was able to reverse engineer enough of one test that was failing to understand it's output.

TEST 48: MEM_Addr_shrts

This test is normally used to check for shorted address lines. It will fill the memory with a pattern first, then it will check each word in order to see if it is still the same pattern. After checking a word, it will check the CMCTL status register to ensure there were no detected errors. Then it will replace the word with another pattern (usually mostly an inverse of the first pattern).

If any address line is shorted, when the test writes the second pattern, it will affect another location in memory. When that location is encountered, it will read as the wrong data thus showing the issue. However, the test is also capable of detecting stuck bits the way it is designed, and this test happened to find all DRAM errors in my case.

The output when the test encounters an error looks like the following:

>>>t 48 ?48 2 08 FF 00 0002 P1=00000000 P2=04000000 P3=00000004 P4=00031000 P5=AAAAAAAA P6=55555555 P7=00000043 P8=200C5875 P9=00000000 P10=2005311F r0=45555555 r1=000C5860 r2=45555555 r3=00000004 r4=0000006B r5=AAAAAAAA r6=20080140 r7=20080144 r8=00000000 ERF=80000000 Normal operation not possible. >>>

I figured out the meaning of some of these registers for this test. First of all, P10 indicates an address where presumably DEC personnel would check a source listing to find out the exact meaning of the rest of the values shown. The meanings of the registers I have found are only valid for this routine, located near 2005311F.

| register | description |

| r0 | contents of memory at address being tested |

| r1 | address being tested |

| r2 | expected pattern from memory being tested |

| r5 | pattern to replace location with |

| r6 | address of CMCTL MEMCSR16 (a diagnostic register) |

| P8 | contents of MEMCSR16 |

MEMCSR16 Register

The MEMCSR16 register gives us information on what kind of memory failure occurred. The bit meanings are as follows, according to the KA650 technical manual:

| bits | description |

| <31> | set if uncorrectable error occurred |

| <30> | set if multiple uncorrectable errors occurred |

| <29> | set if correctable error occurred |

| <28:9> | page address where error occurred (pages are 512 bytes) |

| <8> | set if error ocurred during DMA |

| <7> | set if CDAL bus parity error occurred |

| <6:0> | error syndrome: a unique combination is produced here for each possible single bit error |

writing 1s to bits 31, 30, 29, 8, or 7 of MEMCSR16 resets those bits. bits 28:9 and 6:0 are read only.

The MEMCSR registers can be read with test 9c.

Error Syndrome Field

The error syndrome is particularly useful for troubleshooting memory errors as it can tell us exactly which bit had the error. A list of the syndromes and the corresponding bit error is given below.

| syndrome | bit position or error description |

| 0000000 | no error |

| 0000001 | 32 |

| 0000010 | 33 |

| 0000100 | 34 |

| 0000111 | result of incorrect check bits written on CDAL parity error |

| 0001000 | 35 |

| 0010000 | 36 |

| 0011001 | 7 |

| 0011010 | 2 |

| 0011100 | 1 |

| 0011111 | 4 |

| 0100000 | 37 |

| 0101001 | 15 |

| 0101010 | 10 |

| 0101100 | 9 |

| 0101111 | 12 |

| 0110001 | 23 |

| 0110010 | 18 |

| 0110100 | 17 |

| 0110111 | 20 |

| 0111000 | 24 |

| 0111011 | 29 |

| 0111101 | 30 |

| 0111110 | 27 |

| 1000000 | 38 |

| 1011000 | 0 |

| 1011011 | 5 |

| 1011101 | 6 |

| 1011110 | 3 |

| 1101000 | 8 |

| 1101011 | 13 |

| 1101101 | 14 |

| 1101110 | 11 |

| 1110000 | 16 |

| 1110011 | 21 |

| 1110101 | 22 |

| 1110110 | 19 |

| 1111001 | 31 |

| 1111010 | 26 |

| 1111100 | 25 |

| 1111111 | 28 |

| other | multibit error |

Troubleshooting

We now have all of the information necessary to narrow down which bits in which address regions are bad. However, that doesn't do any good for repair unless we also know which physical DRAMs that bit and region correspond to.

MS650-AA

Shown below is a diagram of the MS650-AA RAM card, broken up into 11 columns and 37 rows. Each spot in this grid contains up to 1 DRAM, but some locations contain other circuitry instead.

| A | B | C | D | E | F | G | H | I | J | K |

--------------------------------------------------------------------------------

01 | ooooooooooooooooooooooooo |DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD| 01

| --------- --------- --------- --------- |DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD|

| |BBBBBBB| |BBBBBBB| |BBBBBBB| |BBBBBBB| |DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD|

| |BBBBBBB| |BBBBBBB| |BBBBBBB| |BBBBBBB| |DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD|

08 | --------- --------- --------- --------- |DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD| 08

|-------------------------------------------DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD|

09 |DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD| 09

|DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD|

16 |DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD| 16

17 |DDDDDDD-----------------------------DDDDDDDDDDDDD-----------------------------| 17

18 |DDDDDDD|TTTTTTT TTTTTTTTT TTTTTTTT |DDDDDDDDDDDDD|TTTTTTTT TTTTTTTTT TTTTTTTT | 18

19 |DDDDDDD-----------------------------DDDDDDDDDDDDD-----------------------------| 19

20 |DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD| 20

|DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD|

|DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD|

|DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD|

|DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD|

|DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD|

|DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD|

32 |DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD| 32

33 |DDDDDDD-----------------------------DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD| 33

36 |DDDDDDD| PPPPPPP TTTTT TTTTT |DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD| 35

37 |-------- TTTTTTT TTTTTTT --------DDDDDDDDDDDDDD-------DDDDDDDDDDDDDD| 37

| -------------- --------------|

| ___- - ___- |

| | | || | | |

-------------------- ----------------------------------------------------------

| A | B | C | D | E | F | G | H | I | J | K |

-----------------------------------------------

| D DRAMS |

| T TTL IC |

| B some kind of DEC custom fast data buffer? |

| P PAL16L8 |

| o data connector |

| | border |

| - border |

-----------------------------------------------

The MS650-AA RAM card uses two RAS lines. During normal initialization of the VAX, the rank connected to RAS0 will be first in memory, followed by the rank connected to RAS1. Presumably, the MS650-BA card would have 4 ranks.

RAS0 - first 4MB RAS1 - second 4MB

Based on the bit with the error, as well as the memory region where the error occurred, the specific DRAM with the failure can be found and replaced.

Below is a list of the DRAMs sorted by memory region and bit, showing the grid location of the DRAM IC.

By using the built in tests, along with MEMCSR16, and perhaps some manual DEPOSIT and EXAMINE testing, the bad DRAM should be possible to locate and then, using this table, the DRAM can be replaced.

| DRAM | Address | data bit |

| A12 | 0XXXXX | MD00 |

| A11 | 1XXXXX | MD00 |

| A10 | 2XXXXX | MD00 |

| A09 | 3XXXXX | MD00 |

| A16 | 4XXXXX | MD00 |

| A15 | 5XXXXX | MD00 |

| A14 | 6XXXXX | MD00 |

| A13 | 7XXXXX | MD00 |

| A24 | 0XXXXX | MD01 |

| A23 | 1XXXXX | MD01 |

| A22 | 2XXXXX | MD01 |

| A21 | 3XXXXX | MD01 |

| A20 | 4XXXXX | MD01 |

| A19 | 5XXXXX | MD01 |

| A18 | 6XXXXX | MD01 |

| A17 | 7XXXXX | MD01 |

| A32 | 0XXXXX | MD02 |

| A31 | 1XXXXX | MD02 |

| A30 | 2XXXXX | MD02 |

| A29 | 3XXXXX | MD02 |

| A28 | 4XXXXX | MD02 |

| A27 | 5XXXXX | MD02 |

| A26 | 6XXXXX | MD02 |

| A25 | 7XXXXX | MD02 |

| B12 | 0XXXXX | MD03 |

| B11 | 1XXXXX | MD03 |

| B10 | 2XXXXX | MD03 |

| B09 | 3XXXXX | MD03 |

| A36 | 4XXXXX | MD03 |

| A35 | 5XXXXX | MD03 |

| A34 | 6XXXXX | MD03 |

| A33 | 7XXXXX | MD03 |

| B24 | 0XXXXX | MD04 |

| B23 | 1XXXXX | MD04 |

| B22 | 2XXXXX | MD04 |

| B21 | 3XXXXX | MD04 |

| B16 | 4XXXXX | MD04 |

| B15 | 5XXXXX | MD04 |

| B14 | 6XXXXX | MD04 |

| B13 | 7XXXXX | MD04 |

| B32 | 0XXXXX | MD05 |

| B31 | 1XXXXX | MD05 |

| B30 | 2XXXXX | MD05 |

| B29 | 3XXXXX | MD05 |

| B28 | 4XXXXX | MD05 |

| B27 | 5XXXXX | MD05 |

| B26 | 6XXXXX | MD05 |

| B25 | 7XXXXX | MD05 |

| C12 | 0XXXXX | MD06 |

| C11 | 1XXXXX | MD06 |

| C10 | 2XXXXX | MD06 |

| C09 | 3XXXXX | MD06 |

| C16 | 4XXXXX | MD06 |

| C15 | 5XXXXX | MD06 |

| C14 | 6XXXXX | MD06 |

| C13 | 7XXXXX | MD06 |

| C24 | 0XXXXX | MD07 |

| C23 | 1XXXXX | MD07 |

| C22 | 2XXXXX | MD07 |

| C21 | 3XXXXX | MD07 |

| E20 | 4XXXXX | MD07 |

| D20 | 5XXXXX | MD07 |

| C20 | 6XXXXX | MD07 |

| B20 | 7XXXXX | MD07 |

| C32 | 0XXXXX | MD08 |

| C31 | 1XXXXX | MD08 |

| C30 | 2XXXXX | MD08 |

| C29 | 3XXXXX | MD08 |

| C28 | 4XXXXX | MD08 |

| C27 | 5XXXXX | MD08 |

| C26 | 6XXXXX | MD08 |

| C25 | 7XXXXX | MD08 |

| D32 | 0XXXXX | MD09 |

| D31 | 1XXXXX | MD09 |

| D30 | 2XXXXX | MD09 |

| D29 | 3XXXXX | MD09 |

| D28 | 4XXXXX | MD09 |

| D27 | 5XXXXX | MD09 |

| D26 | 6XXXXX | MD09 |

| D25 | 7XXXXX | MD09 |

| D24 | 0XXXXX | MD10 |

| D23 | 1XXXXX | MD10 |

| D22 | 2XXXXX | MD10 |

| D21 | 3XXXXX | MD10 |

| D16 | 4XXXXX | MD10 |

| D15 | 5XXXXX | MD10 |

| D14 | 6XXXXX | MD10 |

| D13 | 7XXXXX | MD10 |

| D12 | 0XXXXX | MD11 |

| D11 | 1XXXXX | MD11 |

| D10 | 2XXXXX | MD11 |

| D09 | 3XXXXX | MD11 |

| E16 | 4XXXXX | MD11 |

| E15 | 5XXXXX | MD11 |

| E14 | 6XXXXX | MD11 |

| E13 | 7XXXXX | MD11 |

| E12 | 0XXXXX | MD12 |

| E11 | 1XXXXX | MD12 |

| E10 | 2XXXXX | MD12 |

| E09 | 3XXXXX | MD12 |

| E28 | 4XXXXX | MD12 |

| E27 | 5XXXXX | MD12 |

| E26 | 6XXXXX | MD12 |

| E25 | 7XXXXX | MD12 |

| E24 | 0XXXXX | MD13 |

| E23 | 1XXXXX | MD13 |

| E22 | 2XXXXX | MD13 |

| E21 | 3XXXXX | MD13 |

| F16 | 4XXXXX | MD13 |

| F15 | 5XXXXX | MD13 |

| F14 | 6XXXXX | MD13 |

| F13 | 7XXXXX | MD13 |

| E32 | 0XXXXX | MD14 |

| E31 | 1XXXXX | MD14 |

| E30 | 2XXXXX | MD14 |

| E29 | 3XXXXX | MD14 |

| F20 | 4XXXXX | MD14 |

| F19 | 5XXXXX | MD14 |

| F18 | 6XXXXX | MD14 |

| F17 | 7XXXXX | MD14 |

| F32 | 0XXXXX | MD15 |

| F31 | 1XXXXX | MD15 |

| F30 | 2XXXXX | MD15 |

| F29 | 3XXXXX | MD15 |

| F28 | 4XXXXX | MD15 |

| F27 | 5XXXXX | MD15 |

| F26 | 6XXXXX | MD15 |

| F25 | 7XXXXX | MD15 |

| F24 | 0XXXXX | MD16 |

| F23 | 1XXXXX | MD16 |

| F22 | 2XXXXX | MD16 |

| F21 | 3XXXXX | MD16 |

| F36 | 4XXXXX | MD16 |

| F35 | 5XXXXX | MD16 |

| F34 | 6XXXXX | MD16 |

| F33 | 7XXXXX | MD16 |

| G32 | 0XXXXX | MD17 |

| G31 | 1XXXXX | MD17 |

| G30 | 2XXXXX | MD17 |

| G29 | 3XXXXX | MD17 |

| G36 | 4XXXXX | MD17 |

| G35 | 5XXXXX | MD17 |

| G34 | 6XXXXX | MD17 |

| G33 | 7XXXXX | MD17 |

| G24 | 0XXXXX | MD18 |

| G23 | 1XXXXX | MD18 |

| G22 | 2XXXXX | MD18 |

| G21 | 3XXXXX | MD18 |

| G28 | 4XXXXX | MD18 |

| G27 | 5XXXXX | MD18 |

| G26 | 6XXXXX | MD18 |

| G25 | 7XXXXX | MD18 |

| H32 | 0XXXXX | MD19 |

| H31 | 1XXXXX | MD19 |

| H30 | 2XXXXX | MD19 |

| H29 | 3XXXXX | MD19 |

| G20 | 4XXXXX | MD19 |

| G19 | 5XXXXX | MD19 |

| G18 | 6XXXXX | MD19 |

| G17 | 7XXXXX | MD19 |

| H24 | 0XXXXX | MD20 |

| H23 | 1XXXXX | MD20 |

| H22 | 2XXXXX | MD20 |

| H21 | 3XXXXX | MD20 |

| K37 | 4XXXXX | MD20 |

| J37 | 5XXXXX | MD20 |

| H37 | 6XXXXX | MD20 |

| G37 | 7XXXXX | MD20 |

| I32 | 0XXXXX | MD21 |

| I31 | 1XXXXX | MD21 |

| I30 | 2XXXXX | MD21 |

| I29 | 3XXXXX | MD21 |

| H36 | 4XXXXX | MD21 |

| H35 | 5XXXXX | MD21 |

| H34 | 6XXXXX | MD21 |

| H33 | 7XXXXX | MD21 |

| I24 | 0XXXXX | MD22 |

| I23 | 1XXXXX | MD22 |

| I22 | 2XXXXX | MD22 |

| I21 | 3XXXXX | MD22 |

| H28 | 4XXXXX | MD22 |

| H27 | 5XXXXX | MD22 |

| H26 | 6XXXXX | MD22 |

| H25 | 7XXXXX | MD22 |

| J32 | 0XXXXX | MD23 |

| J31 | 1XXXXX | MD23 |

| J30 | 2XXXXX | MD23 |

| J29 | 3XXXXX | MD23 |

| I36 | 4XXXXX | MD23 |

| I35 | 5XXXXX | MD23 |

| I34 | 6XXXXX | MD23 |

| I33 | 7XXXXX | MD23 |

| J24 | 0XXXXX | MD24 |

| J23 | 1XXXXX | MD24 |

| J22 | 2XXXXX | MD24 |

| J21 | 3XXXXX | MD24 |

| I28 | 4XXXXX | MD24 |

| I27 | 5XXXXX | MD24 |

| I26 | 6XXXXX | MD24 |

| I25 | 7XXXXX | MD24 |

| K32 | 0XXXXX | MD25 |

| K31 | 1XXXXX | MD25 |

| K30 | 2XXXXX | MD25 |

| K29 | 3XXXXX | MD25 |

| J36 | 4XXXXX | MD25 |

| J35 | 5XXXXX | MD25 |

| J34 | 6XXXXX | MD25 |

| J33 | 7XXXXX | MD25 |

| K24 | 0XXXXX | MD26 |

| K23 | 1XXXXX | MD26 |

| K22 | 2XXXXX | MD26 |

| K21 | 3XXXXX | MD26 |

| J28 | 4XXXXX | MD26 |

| J27 | 5XXXXX | MD26 |

| J26 | 6XXXXX | MD26 |

| J25 | 7XXXXX | MD26 |

| K20 | 0XXXXX | MD27 |

| J20 | 1XXXXX | MD27 |

| I20 | 2XXXXX | MD27 |

| H20 | 3XXXXX | MD27 |

| K36 | 4XXXXX | MD27 |

| K35 | 5XXXXX | MD27 |

| K34 | 6XXXXX | MD27 |

| K33 | 7XXXXX | MD27 |

| F12 | 0XXXXX | MD28 |

| F11 | 1XXXXX | MD28 |

| F10 | 2XXXXX | MD28 |

| F09 | 3XXXXX | MD28 |

| K28 | 4XXXXX | MD28 |

| K26 | 6XXXXX | MD28 |

| K27 | 5XXXXX | MD28 |

| K25 | 7XXXXX | MD28 |

| G12 | 0XXXXX | MD29 |

| G11 | 1XXXXX | MD29 |

| G10 | 2XXXXX | MD29 |

| G09 | 3XXXXX | MD29 |

| G16 | 4XXXXX | MD29 |

| G15 | 5XXXXX | MD29 |

| G14 | 6XXXXX | MD29 |

| G13 | 7XXXXX | MD29 |

| G04 | 0XXXXX | MD30 |

| G03 | 1XXXXX | MD30 |

| G02 | 2XXXXX | MD30 |

| G01 | 3XXXXX | MD30 |

| G08 | 4XXXXX | MD30 |

| G07 | 5XXXXX | MD30 |

| G06 | 6XXXXX | MD30 |

| G05 | 7XXXXX | MD30 |

| H04 | 0XXXXX | MD31 |

| H03 | 1XXXXX | MD31 |

| H02 | 2XXXXX | MD31 |

| H01 | 3XXXXX | MD31 |

| H08 | 4XXXXX | MD31 |

| H07 | 5XXXXX | MD31 |

| H06 | 6XXXXX | MD31 |

| H05 | 7XXXXX | MD31 |

| H12 | 0XXXXX | MD32 |

| H11 | 1XXXXX | MD32 |

| H10 | 2XXXXX | MD32 |

| H09 | 3XXXXX | MD32 |

| H16 | 4XXXXX | MD32 |

| H15 | 5XXXXX | MD32 |

| H14 | 6XXXXX | MD32 |

| H13 | 7XXXXX | MD32 |

| I04 | 0XXXXX | MD33 |

| I03 | 1XXXXX | MD33 |

| I02 | 2XXXXX | MD33 |

| I01 | 3XXXXX | MD33 |

| I08 | 4XXXXX | MD33 |

| I07 | 5XXXXX | MD33 |

| I06 | 6XXXXX | MD33 |

| I05 | 7XXXXX | MD33 |

| I12 | 0XXXXX | MD34 |

| I11 | 1XXXXX | MD34 |

| I10 | 2XXXXX | MD34 |

| I09 | 3XXXXX | MD34 |

| I16 | 4XXXXX | MD34 |

| I15 | 5XXXXX | MD34 |

| I14 | 6XXXXX | MD34 |

| I13 | 7XXXXX | MD34 |

| J04 | 0XXXXX | MD35 |

| J03 | 1XXXXX | MD35 |

| J02 | 2XXXXX | MD35 |

| J01 | 3XXXXX | MD35 |

| J08 | 4XXXXX | MD35 |

| J07 | 5XXXXX | MD35 |

| J06 | 6XXXXX | MD35 |

| J05 | 7XXXXX | MD35 |

| J12 | 0XXXXX | MD36 |

| J11 | 1XXXXX | MD36 |

| J10 | 2XXXXX | MD36 |

| J09 | 3XXXXX | MD36 |

| J16 | 4XXXXX | MD36 |

| J15 | 5XXXXX | MD36 |

| J14 | 6XXXXX | MD36 |

| J13 | 7XXXXX | MD36 |

| K04 | 0XXXXX | MD37 |

| K03 | 1XXXXX | MD37 |

| K02 | 2XXXXX | MD37 |

| K01 | 3XXXXX | MD37 |

| K08 | 4XXXXX | MD37 |

| K07 | 5XXXXX | MD37 |

| K06 | 6XXXXX | MD37 |

| K05 | 7XXXXX | MD37 |

| K12 | 0XXXXX | MD38 |

| K11 | 1XXXXX | MD38 |

| K10 | 2XXXXX | MD38 |

| K09 | 3XXXXX | MD38 |

| K16 | 4XXXXX | MD38 |

| K15 | 5XXXXX | MD38 |

| K14 | 6XXXXX | MD38 |

| K13 | 7XXXXX | MD38 |

MS650-BA

Because I did not have an MS650-BA to test, I do not have as much information on this module as on the MS650-AA. Presumably, the MS650-BA has 4 ranks of 4MB in 1MBxX DRAMs, meaning there is no need to have 4 banks in each rank like the 256kx1 DRAMs on the MS650-AA.