Difference between revisions of "KA750 CPU"

m (+750 block diag) |

(Move impl technology to main 750 article; add PCS) |

||

| Line 1: | Line 1: | ||

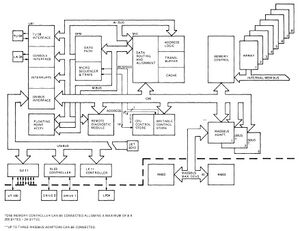

[[Image:VAX750block.jpg|right|thumb|300px|VAX-11/750 system block diagram, showing the major KA750 functional units]] | [[Image:VAX750block.jpg|right|thumb|300px|VAX-11/750 system block diagram, showing the major KA750 functional units]] | ||

| − | The '''KA750 CPU''' was the [[Central Processing Unit|CPU]] of the [[VAX-11/750]].It was a [[synchronous]] [[microcode]]d design. | + | The '''KA750 CPU''' was the [[Central Processing Unit|CPU]] of the [[VAX-11/750]].It was a [[synchronous]] [[microcode]]d design. Internally, there were several main [[bus]]ses connecting together functional units within the CPU: |

| − | |||

| − | Internally, there were several main [[bus]]ses connecting together functional units within the CPU: | ||

* MBus | * MBus | ||

| Line 10: | Line 8: | ||

* RBus | * RBus | ||

| − | The MBus and WBus are [[tri-state]], 32 bits wide; fields in the micro-[[instruction]]s specify the source | + | The MBus and WBus are [[tri-state]], 32 bits wide; fields in the micro-[[instruction]]s specify the source which will use each bus on each cycle. The RBus connects scratchpad [[register]]s to the [[arithmetic logic unit|ALU]] and 'super rotator'. |

Microcode supported micro-[[subroutine]]s, up to 15 levels deep. | Microcode supported micro-[[subroutine]]s, up to 15 levels deep. | ||

| Line 21: | Line 19: | ||

* L0003 Memory Interconnect (MIC) - [[virtual memory]] translation buffer, [[cache]], [[main memory]] interface | * L0003 Memory Interconnect (MIC) - [[virtual memory]] translation buffer, [[cache]], [[main memory]] interface | ||

* L0004 [[UNIBUS]] Interface (UBI) - UNIBUS control and function, ancillary functions | * L0004 [[UNIBUS]] Interface (UBI) - UNIBUS control and function, ancillary functions | ||

| − | * L0005 CPU Control Store (CCS) - microcode [[read-only memory|ROMs]], interface to optional | + | * L0005 CPU Control Store (CCS) - microcode [[read-only memory|ROMs]], interface to optional KU750 Writable Control Store (WCS - sometimes informally called the User Control Store - on a [[daughter-board]] of the CCS) |

| − | + | The L0005 CCS was later replaced by the L0008 Patchable Control Store (PCS). Originally, the concept was that the KA750's microcode would not change often, so it was stored in [[read-only memory|PROM (unlike the [[KL10]] and [[KA780 CPU|KA780]]). This turned out to be incorrect; like most software, bugs were found regularly. The PCS is designed to store the basic microcode in PROM, but to allow it to be 'patched' dynamically. | |

| + | |||

| + | CPU options use other boards: | ||

* L0006 - Remote Diagnostic Module (RDM) | * L0006 - Remote Diagnostic Module (RDM) | ||

| − | * L0001 - Floating-Point Accelerator (FPA) | + | * L0001 - FP750 Floating-Point Accelerator (FPA) |

| + | |||

| + | The base CPU does support [[floating point]], but implemented entirely in microcode; the FP750 increases floating-point performance substantially. | ||

{{semi-stub}} | {{semi-stub}} | ||

Revision as of 17:47, 3 June 2022

The KA750 CPU was the CPU of the VAX-11/750.It was a synchronous microcoded design. Internally, there were several main busses connecting together functional units within the CPU:

- MBus

- WBus

- Control store address (CSA)

- RBus

The MBus and WBus are tri-state, 32 bits wide; fields in the micro-instructions specify the source which will use each bus on each cycle. The RBus connects scratchpad registers to the ALU and 'super rotator'.

Microcode supported micro-subroutines, up to 15 levels deep.

Components

The basic KA750 was implemented in four large PCBs:

- L0002 Data Path Module (DPM) - arithmetical and logical functions, micro-sequencer

- L0003 Memory Interconnect (MIC) - virtual memory translation buffer, cache, main memory interface

- L0004 UNIBUS Interface (UBI) - UNIBUS control and function, ancillary functions

- L0005 CPU Control Store (CCS) - microcode ROMs, interface to optional KU750 Writable Control Store (WCS - sometimes informally called the User Control Store - on a daughter-board of the CCS)

The L0005 CCS was later replaced by the L0008 Patchable Control Store (PCS). Originally, the concept was that the KA750's microcode would not change often, so it was stored in [[read-only memory|PROM (unlike the KL10 and KA780). This turned out to be incorrect; like most software, bugs were found regularly. The PCS is designed to store the basic microcode in PROM, but to allow it to be 'patched' dynamically.

CPU options use other boards:

- L0006 - Remote Diagnostic Module (RDM)

- L0001 - FP750 Floating-Point Accelerator (FPA)

The base CPU does support floating point, but implemented entirely in microcode; the FP750 increases floating-point performance substantially.