Difference between revisions of "Extended Memory Interconnect"

m (+cat, for finding) |

(Improve description) |

||

| Line 1: | Line 1: | ||

| − | The '''Extended Memory Interconnect''' (usually given as the acronym: '''XMI''') was a [[bus]] introduced with the [[VAX 6000 series]] | + | The '''Extended Memory Interconnect''' (usually given as the acronym: '''XMI''') was a [[bus]] introduced with the [[VAX 6000 series]], and also used in later [[Digital Equipment Corporation|DEC]] [[VAX]] computers, to cope with increased requirements, e.g bandwidth. |

| − | == | + | ==Overview== |

| − | |||

| − | + | The XMI bus supports multiple processors, multiple memory modules, and multiple I/O adapters. It consists of: | |

| − | [[ | + | * the electrical environment of the XMI bus, |

| + | * the [[protocol]] observed by a node on the bus, | ||

| + | * the [[backplane]], and | ||

| + | * the [[logic]] used to implement the protocol. | ||

| − | The XMI | + | The XMI is limited length, [[synchronous]], and has centralized [[arbitration]] (individual [[bus grant line]]s run from the arbitrator to each slot in the backplane). Arbitration and data transfers use logically separate divisions of the bus, so they can occur in parallel. |

| − | + | It is also 'pended', which means that an operation can be left in an incomplete state, to allow other entities to use the bus. Several transactions can thus be in progress at any time, rather than forcing later operations to wait for the completion of an earlier operation before they can begin; this allows highly efficient use of the bus bandwidth. | |

| + | |||

| + | The XMI is the primary interconnect for the [[VAX 6000 Model 200|VAX 6200]] system. | ||

| + | |||

| + | [[File:VAX 6200 Four-Processor System Block Diagram.png|thumb|400px|left|A four-processor VAX 6200 system]] | ||

| + | <br clear=all> | ||

| + | |||

| + | The XMI supports: | ||

| − | |||

* Quadword-, octaword-, and hexword-length reads to memory | * Quadword-, octaword-, and hexword-length reads to memory | ||

* Quadword- and octaword-length memory writes | * Quadword- and octaword-length memory writes | ||

| Line 19: | Line 27: | ||

The longword operations implement byte and word modes required by certain I/O devices. | The longword operations implement byte and word modes required by certain I/O devices. | ||

| − | The XMI has a 64 ns bus cycle. | + | The XMI has a 64 ns bus cycle. It has a bandwidth of 100 Mbytes per second; however, the usable bandwidth depends on transaction length: |

| − | |||

| − | |||

{| class="wikitable" | {| class="wikitable" | ||

| Line 43: | Line 49: | ||

|} | |} | ||

| − | == XMI Versions == | + | ==XMI Versions== |

| + | |||

The XMI bus started with the "+5V '''XMI-1'''" version which was developed to the "+3.3V '''XMI-2'''" version later on. | The XMI bus started with the "+5V '''XMI-1'''" version which was developed to the "+3.3V '''XMI-2'''" version later on. | ||

| − | There was an upgrade kit option H9657-CU that takes a VAX 6000 Model 200, 300, or 400 system with an XMI-1 power system and upgrades it to a VAX 6000 Model 500 with an XMI-2 power system. | + | There was an upgrade kit option H9657-CU that takes a VAX 6000 Model 200, 300, or 400 system with an XMI-1 power system and upgrades it to a VAX 6000 Model 500 with an XMI-2 power system. The upgrade adds +3.3 volt power, an XMI-2 backplane preassembled with bus bars and cables, and an H7206-B power and logic unit. |

| − | |||

| − | The upgrade adds +3.3 volt power, an XMI-2 | ||

| − | |||

| − | |||

{{semi-stub}} | {{semi-stub}} | ||

| Line 57: | Line 60: | ||

* [http://www.bitsavers.org/pdf/dec/vax/6200/EK-620AA-TM-001_Tech_May88.pdf VAX 6200 Technical User's Guide] (EK-620AA-TM-001) - the XMI is covered in Chapter 2, pp. 37-91 of the PDF | * [http://www.bitsavers.org/pdf/dec/vax/6200/EK-620AA-TM-001_Tech_May88.pdf VAX 6200 Technical User's Guide] (EK-620AA-TM-001) - the XMI is covered in Chapter 2, pp. 37-91 of the PDF | ||

| + | * [http://www.vaxhaven.com/images/f/fc/EK-650EB-UP-002.pdf EK-650EB-UP-002 VAX 6000 XMI Conversion Manual] | ||

[[Category: DEC Buses]] | [[Category: DEC Buses]] | ||

[[Category: XMI]] | [[Category: XMI]] | ||

[[Category: VAXen]] | [[Category: VAXen]] | ||

Revision as of 12:00, 18 March 2023

The Extended Memory Interconnect (usually given as the acronym: XMI) was a bus introduced with the VAX 6000 series, and also used in later DEC VAX computers, to cope with increased requirements, e.g bandwidth.

Overview

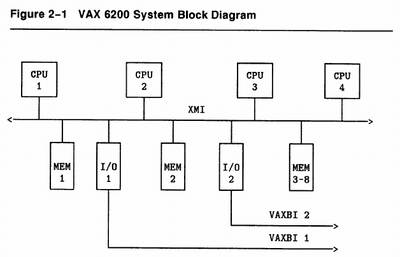

The XMI bus supports multiple processors, multiple memory modules, and multiple I/O adapters. It consists of:

- the electrical environment of the XMI bus,

- the protocol observed by a node on the bus,

- the backplane, and

- the logic used to implement the protocol.

The XMI is limited length, synchronous, and has centralized arbitration (individual bus grant lines run from the arbitrator to each slot in the backplane). Arbitration and data transfers use logically separate divisions of the bus, so they can occur in parallel.

It is also 'pended', which means that an operation can be left in an incomplete state, to allow other entities to use the bus. Several transactions can thus be in progress at any time, rather than forcing later operations to wait for the completion of an earlier operation before they can begin; this allows highly efficient use of the bus bandwidth.

The XMI is the primary interconnect for the VAX 6200 system.

The XMI supports:

- Quadword-, octaword-, and hexword-length reads to memory

- Quadword- and octaword-length memory writes

- Longword-length read and write operations to I/O space

The longword operations implement byte and word modes required by certain I/O devices.

The XMI has a 64 ns bus cycle. It has a bandwidth of 100 Mbytes per second; however, the usable bandwidth depends on transaction length:

| Usable XMI Bandwidth | |

| Operation | Bandwidth (Mbytes/second) |

| Longword (4 bytes) Read | 31.25 |

| Quadword (8 bytes) Read | 62.50 |

| Octaword (16 bytes) Read | 83.30 |

| Hexword (32 bytes) Read | 100.00 |

| Longword Write | 31.25 |

| Quadword Write | 62.50 |

| Octaword Write | 83.30 |

XMI Versions

The XMI bus started with the "+5V XMI-1" version which was developed to the "+3.3V XMI-2" version later on.

There was an upgrade kit option H9657-CU that takes a VAX 6000 Model 200, 300, or 400 system with an XMI-1 power system and upgrades it to a VAX 6000 Model 500 with an XMI-2 power system. The upgrade adds +3.3 volt power, an XMI-2 backplane preassembled with bus bars and cables, and an H7206-B power and logic unit.

External links

- VAX 6200 Technical User's Guide (EK-620AA-TM-001) - the XMI is covered in Chapter 2, pp. 37-91 of the PDF

- EK-650EB-UP-002 VAX 6000 XMI Conversion Manual