Difference between revisions of "Digital Storage Systems Interconnect"

m (→External Links: broken URL) |

(Describe use of DSSI to produce loosely-couple VAX multi-processor) |

||

| Line 1: | Line 1: | ||

| − | The '''Digital Storage Systems Interconnect''' (usually given as '''DSSI''') is a [[mass storage]] [[bus]] from [[Digital Equipment Corporation|DEC]]. | + | The '''Digital Storage Systems Interconnect''' (usually given as '''DSSI''') is a [[mass storage]] [[bus]] from [[Digital Equipment Corporation|DEC]]. It can also be used to create loosely-couple [[multi-processor]]s by sharing a number of [[disk drive]]s between two systems. Such shared drives are termed ' Integrated Storage Elements' (ISEs). |

| + | |||

| + | [[File:The SCA Model.png|thumb|right|350px|Systems Communication Architecture]] | ||

Description from the 'Digital's Storage System Interconnect' protocol specification document: | Description from the 'Digital's Storage System Interconnect' protocol specification document: | ||

| Line 5: | Line 7: | ||

"The DSSI, supporting the needs of low-end and mid-range systems, is one in a family of high-performance computer-to-computer interconnects ([[Computer Interconnect|CI]]'s) that combine a common host interface and port layer with an implementation-specific datalink and physical interconnect. | "The DSSI, supporting the needs of low-end and mid-range systems, is one in a family of high-performance computer-to-computer interconnects ([[Computer Interconnect|CI]]'s) that combine a common host interface and port layer with an implementation-specific datalink and physical interconnect. | ||

| − | CI-class interconnects provide the transmission services required by Digital's [[Systems Communication Architecture]] (SCA) - a four-tiered set of protocols and interfaces as shown | + | CI-class interconnects provide the transmission services required by Digital's [[Systems Communication Architecture]] (SCA) - a four-tiered set of protocols and interfaces as shown [to the right]." |

| − | [[ | + | The [[QBUS]] DSSI [[peripheral]] was the [[KFQSA]]. Some [[VAX]] [[Central Processing Unit|CPU]]'s had built-in DSSI peripherals, called 'Embedded DSSI Adapters' (EDAs); one such was the [[KA640 CPU]] of the [[MicroVAX 3300/3400]]. The [[VAX 4000 series]] also supported the DSSI. |

{{semi-stub}} | {{semi-stub}} | ||

| − | == External Links == | + | ==External Links== |

| + | |||

* [http://bitsavers.org/pdf/dec/dsa/dssi/ DSSI] - DSSI and related documents at [[Bitsavers]] | * [http://bitsavers.org/pdf/dec/dsa/dssi/ DSSI] - DSSI and related documents at [[Bitsavers]] | ||

** [http://www.bitsavers.org/pdf/dec/dsa/dssi/Digitals_Storage_System_Interconnect_Rev_1.0.0_199003.txt Digital's Storage System Interconnect] - protocol specification document | ** [http://www.bitsavers.org/pdf/dec/dsa/dssi/Digitals_Storage_System_Interconnect_Rev_1.0.0_199003.txt Digital's Storage System Interconnect] - protocol specification document | ||

| + | * [http://www.bitsavers.org/pdf/dec/vax/3800/EK-338AC-DH-003_MicroVAX_Dual-Host_Systems_Dec90.pdf MicroVAX Dual-Host Systems] (EK-338AC-DH-003) - contains a clear description of how a DSSI can be used to create a loosely-couple multi-processor | ||

[[Category: DEC Buses]] | [[Category: DEC Buses]] | ||

[[Category: DEC Mass Storage]] | [[Category: DEC Mass Storage]] | ||

[[Category: DSSI]] | [[Category: DSSI]] | ||

Revision as of 11:02, 25 March 2023

The Digital Storage Systems Interconnect (usually given as DSSI) is a mass storage bus from DEC. It can also be used to create loosely-couple multi-processors by sharing a number of disk drives between two systems. Such shared drives are termed ' Integrated Storage Elements' (ISEs).

Description from the 'Digital's Storage System Interconnect' protocol specification document:

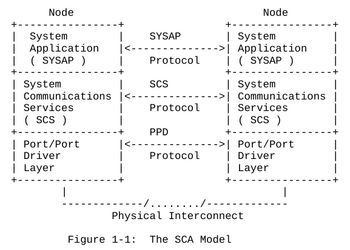

"The DSSI, supporting the needs of low-end and mid-range systems, is one in a family of high-performance computer-to-computer interconnects (CI's) that combine a common host interface and port layer with an implementation-specific datalink and physical interconnect.

CI-class interconnects provide the transmission services required by Digital's Systems Communication Architecture (SCA) - a four-tiered set of protocols and interfaces as shown [to the right]."

The QBUS DSSI peripheral was the KFQSA. Some VAX CPU's had built-in DSSI peripherals, called 'Embedded DSSI Adapters' (EDAs); one such was the KA640 CPU of the MicroVAX 3300/3400. The VAX 4000 series also supported the DSSI.

External Links

- DSSI - DSSI and related documents at Bitsavers

- Digital's Storage System Interconnect - protocol specification document

- MicroVAX Dual-Host Systems (EK-338AC-DH-003) - contains a clear description of how a DSSI can be used to create a loosely-couple multi-processor