KA750 CPU

From Computer History Wiki

The KA750 CPU was the CPU of the VAX-11/750.It was a synchronous microcoded design. It was primarily implemented in gate array chips holding 400 NAND gates; they were configured at manufacture time into the 39 different types used in the /750.

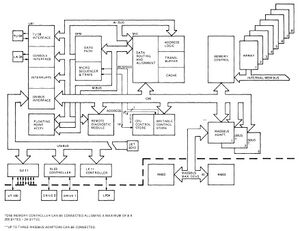

Internally, there were several main busses connecting together functional units within the CPU:

- MBus

- WBus

- Control store address (CSA)

- RBus

The MBus and WBus are tri-state, 32 bits wide; fields in the micro-instructions specify the source using each bus on each cycle. The RBus connects scratchpad registers to the ALU and 'super rotator'.

Microcode supported micro-subroutines, up to 15 levels deep.

Components

The basic KA750 was implemented in four large PCBs:

- L0002 Data Path Module (DPM) - arithmetical and logical functions, micro-sequencer

- L0003 Memory Interconnect (MIC) - virtual memory translation buffer, cache, main memory interface

- L0004 UNIBUS Interface (UBI) - UNIBUS control and function, ancillary functions

- L0005 CPU Control Store (CCS) - microcode ROMs, interface to optional writable control store (WCS)

Options use other boards:

- L0006 - Remote Diagnostic Module (RDM)

- L0001 - Floating-Point Accelerator (FPA)