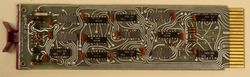

M782 Interrupt Control

The M782 Interrupt Control (later versions M7820 and M7821) is a DEC FLIP CHIP which implements the 'interrupt control' function for the UNIBUS. It contains two separate interrupt circuit blocks; they can be wired to produce separate interrupts, or either can be used to provide the device with DMA capability.

It was used, usually along with an M105 Address Selector, in early PDP-11 device controllers which plugged into an SPC slot. It was also used in a number of early devices which were built out of a custom backplane and a large number of FLIP CHIPs, such as the RK11-C. Some later devices which no longer used a large number of small Flip Chips (such as the TMB11) also used it.

Revisions

This board, unlike the M105, appeared in a plethora of different versions; not just the M782 (above), M7820 (right) and M7821 (below), but also different etch revisions of each, many of which differ very significantly from each other. (The number appears to have been changed for functionality/configuration changes; below).

Although some of the changes are due to functionality changes, it appears that many of them were attempts to get rid of race issues in the grant-passing arbitration circuity, which is often quite different between the versions. The import of the changes is not always completely clear, but the D version of the M7821, the last, contains a number of delay lines not present on the earlier models; this is significant because when the meta-stability issue at the heart of race problems was finally fully understood, it became clear that delays were the only 'solution'.

The M782 seems to have appeared in revisions A though E (it is not known if there was an un-lettered initial version, but that does not seem to have been DEC practise at the time), although examples of the C and D are not extant (it is not known if they actually went into production). The M7820 appears to have had A-C, with only the C extant. The M7821 appears in A-D revisions, with the A not extant: the early one, marked 'M7821B' (below); the C (image here), which is rare; and the D (bottom).

Jumpers

The boards contained a number of jumpers which could be used to set confguration options.

Vectors

One set of jumpers controls the interrupt vector. The M782 can set vector address bits 3-7 (i.e. vectors from 0 through 0374); bit 2 (04) is controlled by the device's circuitry. The M7820 adds bit 8 (0400; i.e. vectors of the form 0xx0 and 0xx4).

(Note: The 1972 Edition of the 'Digital Logic Handbook' shows a jumper on address bit 2; however neither the prints, nor actual boards, agree with this.)

The M7821 adds a jumper on address bit 2 (04); that bit can be controlled by either the device's electronics, or the jumper. (The sense of the vector jumpers is also inverted between the M7821 and the two previous versions; they are 'in' for '1', and 'out' for '0', on the M7821.)

Operation

The M7821 has a number of operational improvements over the M7820. (Note: Not all the non-vector jumpers are on all etch revisions.)

It will decline interrupt grants when there is a DMA request pending, reducing the DMA latency. Not all PDP-11 CPUs can handle this properly; a jumper (un-numbered; it is up near the handle) disables this behaviour when it is removed.

The A interrupt block can allow a device to do multiple DMA cycles with a single bus grant, when pin J2 is left high; grounding pin J2 signals that the DMA cycles are finished.

Images

See also

- Bus Arbitration on the Unibus and QBUS - Goes into detail on the grant-passing race issue, and why a delay is the only 'solution'

External links

- FlipChip Modules - Images and engineering drawings for FLIP CHIP modules