Difference between revisions of "PDP-9 control memory"

From Computer History Wiki

m (→CMA modification) |

(→CMA modification: It's a mess.) |

||

| Line 80: | Line 80: | ||

===CMA modification=== | ===CMA modification=== | ||

| − | The control memory address, CMA, from process word bits 23-28 | + | The control memory address, CMA, from process word bits 23-28 is heavily modified by random logic before being used for addressing the control memory. |

* In address range 00-07 the CMA is '''OR''''ed with a value that depends on the switches: | * In address range 00-07 the CMA is '''OR''''ed with a value that depends on the switches: | ||

| Line 96: | Line 96: | ||

| 6 || START | | 6 || START | ||

|} | |} | ||

| + | |||

| + | * CMA 30 from word 24 is '''OR''''ed with 1 or 2 depending on the result of the TI control bit. | ||

| + | |||

| + | * Data channel requests will similarly "boost" the address. | ||

* In address range 60-77, the lower four bits come from the upper four bits of the instruction register. Hence each process word in this range implements one of the 16 instructions. | * In address range 60-77, the lower four bits come from the upper four bits of the instruction register. Hence each process word in this range implements one of the 16 instructions. | ||

Revision as of 17:01, 22 July 2023

Description of the PDP-9 control memory contents. The control memory is a read-only core memory which consists of 64 process words (i.e. microwords) of 36 bits each.

Contents

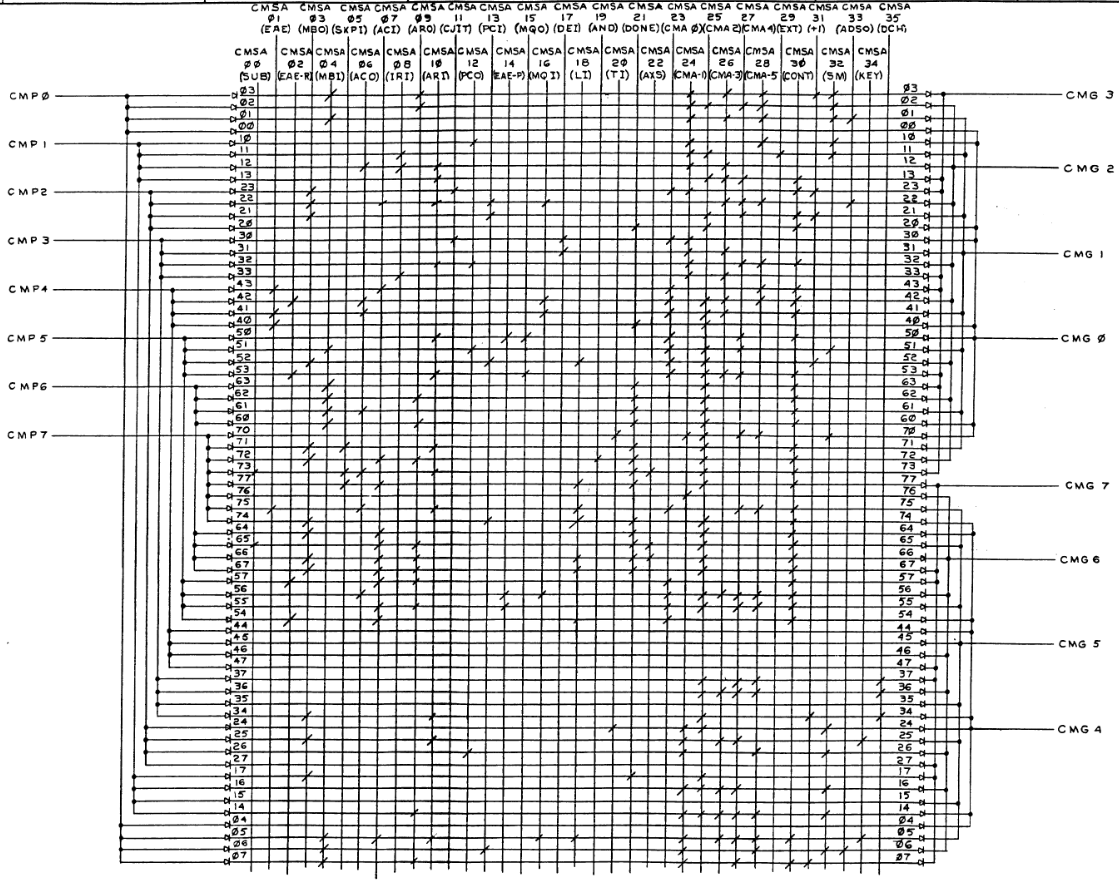

Wiring matrix

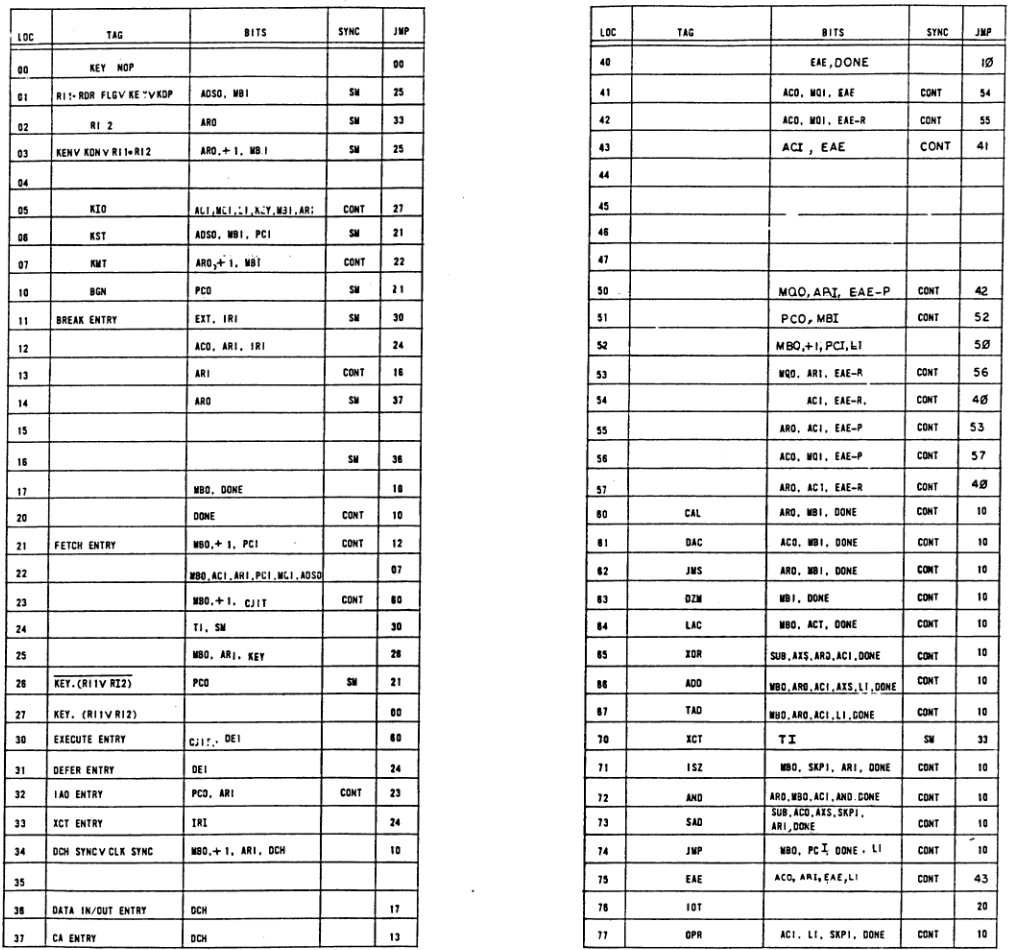

Program listing

Meaning of control bits

| Position | Name | Description |

|---|---|---|

| 00 | SUB | Subtract gate |

| 01 | EAE | |

| 02 | EAE-R | |

| 03 | MBO | Memory buffer output gate |

| 04 | MBI | Memory buffer input gate |

| 05 | SKPI | Skip input |

| 06 | ACO | Accumulator output gate |

| 07 | ACI | Accumulator input gate |

| 08 | IRI | Instruction regster input gate |

| 09 | ARO | Arithmetic register output gate |

| 10 | ARI | Arithmetic register input gate |

| 11 | CJIT | CAL/JMS/interrupt transfer gate |

| 12 | PCO | Program counter output gate |

| 13 | PCI | Program counter input gate |

| 14 | EAE-P | |

| 15 | MQO | Multiplier/quotient output gate |

| 16 | MQI | Multiplier/quotient input gate |

| 17 | DEI | Defer/execute initiate |

| 18 | LI | Link input gate |

| 19 | AND | AND instruction gate |

| 20 | TI | Test for indirect addressing |

| 21 | DONE | Instruction done gate |

| 22 | AXS | ADD/XOR/SAD instruction gate |

| 23-28 | CMA 0-5 | Address for next process word, possibly modified |

| 29 | EXT | External transfer gate (program break) |

| 30 | CONT | Continue to next process word |

| 31 | +1 | Increment the ADR |

| 32 | SM | Start memory cycle |

| 33 | ADSO | Address switches output gate |

| 34 | KEY | Key gate |

| 35 | DCH |

CMA modification

The control memory address, CMA, from process word bits 23-28 is heavily modified by random logic before being used for addressing the control memory.

- In address range 00-07 the CMA is OR'ed with a value that depends on the switches:

| Value | Switch |

|---|---|

| 1 | EXAMINE or DEPOSIT or READ IN |

| 2 | |

| 3 | EXAMINE NEXT or DEPOSIT NEXT or READ IN |

| 5 | IO RESET |

| 6 | START |

- CMA 30 from word 24 is OR'ed with 1 or 2 depending on the result of the TI control bit.

- Data channel requests will similarly "boost" the address.

- In address range 60-77, the lower four bits come from the upper four bits of the instruction register. Hence each process word in this range implements one of the 16 instructions.

Decoded to binary and symbolic form

| Address | Process word bits | Symbolic description |

|---|---|---|

| 00 | 000000000000000000000000000000000000 | CMA/00 |

| 01 | 000010000000000000000000101010001100 | MBI ADSO SM CMA/25 |

| 02 | 000000000100000000000000110110001000 | ARO SM CMA/33 |

| 03 | 000010000100000000000000101010011000 | MBI ARO +1 SM CMA/25 |

| 04 | 000000000000000000000000000000000000 | CMA/00 |

| 05 | 000010010010000010100000101110100010 | MBI ACI ARI MQI LI KEY CONT CMA/27 |

| 06 | 000010000000010000000000100010001100 | MBI PCI ADSO SM CMA/21 |

| 07 | 000010000100000000000000100100110000 | MBI ARO +1 CONT CMA/22 |

| 10 | 000000000000100000000000100010001000 | PCO SM CMA/21 |

| 11 | 000000001000000000000000110001001000 | IRI EXT SM CMA/30 |

| 12 | 000000101010000000000000101000000000 | ACO IRI ARI CMA/24 |

| 13 | 000000000010000000000000011100100000 | ARI CONT CMA/16 |

| 14 | 000000000100000000000000111110001000 | ARO SM CMA/37 |

| 15 | 000000000000000000000000000000000000 | CMA/00 |

| 16 | 000000000000000000000000111100001000 | SM CMA/36 |

| 17 | 000100000000000000000100010000000000 | MBO DONE CMA/10 |

| 20 | 000000000000000000000100010000100000 | DONE CONT CMA/10 |

| 21 | 000100000000010000000000010100110000 | MBO PCI +1 CONT CMA/12 |

| 22 | 000100010010010010000000001110000100 | MBO ACI ARI PCI MQI ADSO CMA/07 |

| 23 | 000100000001000000000001100000110000 | MBO CJIT +1 CONT CMA/60 |

| 24 | 000000000000000000001000110000001000 | TI SM CMA/30 |

| 25 | 000100000010000000000000101100000010 | MBO ARI KEY CMA/26 |

| 26 | 000000000000100000000000100010001000 | PCO SM CMA/21 |

| 27 | 000000000000000000000000000000000000 | CMA/00 |

| 30 | 000000000001000001000001100000000000 | CJIT DEI CMA/60 |

| 31 | 000000000000000001000000101000000000 | DEI CMA/24 |

| 32 | 000000000010100000000000100110100000 | ARI PCO CONT CMA/23 |

| 33 | 000000001000000000000000101000000000 | IRI CMA/24 |

| 34 | 000100000010000000000000010000010001 | MBO ARI +1 DCH CMA/10 |

| 35 | 000000000000000000000000000000000000 | CMA/00 |

| 36 | 000000000000000000000000011110000001 | DCH CMA/17 |

| 37 | 000000000000000000000000010110000001 | DCH CMA/13 |

| 40 | 010000000000000000000100010000000000 | EAE DONE CMA/10 |

| 41 | 010000100000000010000001011000100000 | EAE ACO MQI CONT CMA/54 |

| 42 | 001000100000000010000001011010100000 | EAE-R ACO MQI CONT CMA/55 |

| 43 | 010000010000000000000001000010100000 | EAE ACI CONT CMA/41 |

| 44 | 000000000000000000000000000000000000 | CMA/00 |

| 45 | 000000000000000000000000000000000000 | CMA/00 |

| 46 | 000000000000000000000000000000000000 | CMA/00 |

| 47 | 000000000000000000000000000000000000 | CMA/00 |

| 50 | 000000000010001100000001000100100000 | ARI EAE-P MQO CONT CMA/42 |

| 51 | 000010000000100000000001010100001000 | MBI PCO SM CMA/52 |

| 52 | 000100000000010000100001010000010000 | MBO PCI LI +1 CMA/50 |

| 53 | 001000000010000100000001011100100000 | EAE-R ARI MQO CONT CMA/56 |

| 54 | 001000010000000000000001000000100000 | EAE-R ACI CONT CMA/40 |

| 55 | 000000010100001000000001010110100000 | ACI ARO EAE-P CONT CMA/53 |

| 56 | 000000100000001010000001011110100000 | ACO EAE-P MQI CONT CMA/57 |

| 57 | 001000010100000000000001000000100000 | EAE-R ACI ARO CONT CMA/40 |

| 60 | 000010000100000000000100010000100000 | MBI ARO DONE CONT CMA/10 |

| 61 | 000010100000000000000100010000100000 | MBI ACO DONE CONT CMA/10 |

| 62 | 000010000100000000000100010000100000 | MBI ARO DONE CONT CMA/10 |

| 63 | 000010000000000000000100010000100000 | MBI DONE CONT CMA/10 |

| 64 | 000100010000000000000100010000100000 | MBO ACI DONE CONT CMA/10 |

| 65 | 100000010100000000000110010000100000 | SUB ACI ARO DONE AXS CONT CMA/10 |

| 66 | 000100010100000000100110010000100000 | MBO ACI ARO LI DONE AXS CONT CMA/10 |

| 67 | 000100010100000000100100010000100000 | MBO ACI ARO LI DONE CONT CMA/10 |

| 70 | 000000000000000000001000110110001000 | TI SM CMA/33 |

| 71 | 000101000010000000000100010000100000 | MBO SKPI ARI DONE CONT CMA/10 |

| 72 | 000100010100000000010100010000100000 | MBO ACI ARO AND DONE CONT CMA/10 |

| 73 | 100001100010000000000110010000100000 | SUB SKPI ACO ARI DONE AXS CONT CMA/10 |

| 74 | 000100000000010000100100010000100000 | MBO PCI LI DONE CONT CMA/10 |

| 75 | 010000100010000000100001000110100000 | EAE ACO ARI LI CONT CMA/43 |

| 76 | 000000000000000000000000100000000000 | CMA/20 |

| 77 | 000001010000000000100100010000100000 | SKPI ACI LI DONE CONT CMA/10 |