Difference between revisions of "KD11-D CPU"

(Mention PROM use, →External links: +manual, FMPS) |

(mention common KY11/CPU interface) |

||

| Line 9: | Line 9: | ||

It plugs into a modified [[Modified UNIBUS Device|MUD]] [[backplane]], either the the [[DD11-C backplane|DD11-C]] or [[DD11-D backplane]]s, or the special [[DD11-P backplane]] of the [[PDP-11/34]]. | It plugs into a modified [[Modified UNIBUS Device|MUD]] [[backplane]], either the the [[DD11-C backplane|DD11-C]] or [[DD11-D backplane]]s, or the special [[DD11-P backplane]] of the [[PDP-11/34]]. | ||

| − | It supported the [[KY11-LA Operator's Console]] and the [[KY11-LB Programmer's Console]], including the latter's maintenance functionality which allowed the CPU's microcode to be [[single-step]]ped. | + | It supported the [[KY11-LA Operator's Console]] and the [[KY11-LB Programmer's Console]], including the latter's maintenance functionality which allowed the CPU's microcode to be [[single-step]]ped. The KD11-D uses the same [[KY11 to CPU interface]] as the other machines that use them. |

==KY11-LB Interface== | ==KY11-LB Interface== | ||

| Line 20: | Line 20: | ||

* [http://www.bitsavers.org/pdf/dec/pdp11/1104/MP00019_1104_EngrDrws_Feb78.pdf PDP-11/04 engineering drawings] - Contains KD11-D Field Maintenance Print Set (MP00020) on pp. 167-276 (includes complete PROM dumps) | * [http://www.bitsavers.org/pdf/dec/pdp11/1104/MP00019_1104_EngrDrws_Feb78.pdf PDP-11/04 engineering drawings] - Contains KD11-D Field Maintenance Print Set (MP00020) on pp. 167-276 (includes complete PROM dumps) | ||

| − | + | [[Category: PDP-11 Processors]] | |

| − | + | [[Category: UNIBUS Processors]] | |

| − | [[Category:PDP-11 Processors]] | ||

| − | [[Category:UNIBUS Processors]] | ||

Revision as of 13:19, 27 February 2022

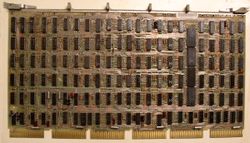

The KD11-D PDP-11 CPU of the PDP-11/04 was a micro-programmed processor (making heavy use of PROMs). It was contained on single hex card (the M7263), the first PDP-11 CPU to be built on a single card.

Like other early, low-cost PDP-11s, it did not support either memory management of any kind, or hardware floating point, EIS instructions, or the various instructions added to the PDP-11 instruction set (XOR, SOB, SXT and MARK).

There is a lack of clarity over the RTT instruction; the pdp11 04/05/10/35/40/45 processor handbook says it is not implemented, but the PDP-11 Architecture Handbook says "available in 11/04 but is different from other implementations"; the KD11-D Processor Manual (EK-KD11D-TM-PRE) says the "first instruction after RTT is guaranteed to be executed" - the same as the KD11-A CPU.

It plugs into a modified MUD backplane, either the the DD11-C or DD11-D backplanes, or the special DD11-P backplane of the PDP-11/34.

It supported the KY11-LA Operator's Console and the KY11-LB Programmer's Console, including the latter's maintenance functionality which allowed the CPU's microcode to be single-stepped. The KD11-D uses the same KY11 to CPU interface as the other machines that use them.

KY11-LB Interface

The microcode diagnostic interface to the KY11-LB is carried over a 10-wire flat cable connected to the J2 Berg connector header on the KY11-LB's M7859 module (the other 10-pin header on that card is unused with the -11/04), and a set of vertical pins in the upper left-hand corner (see image above) of the M7263. (The main functionality of the KY11-B is done over the UNIBUS, and a pair of backplane lines.)

External links

- KD11-D Processor Manual (PDP-11/04) (EK-KD11D-TM-PRE)

- PDP-11/04 engineering drawings - Contains KD11-D Field Maintenance Print Set (MP00020) on pp. 167-276 (includes complete PROM dumps)