Difference between revisions of "DP11-A Synchronous Line Interface"

(→Implementation: +board images) |

m (New cat scheme) |

||

| (5 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

| − | The ''' DP11-A''' is the earliest [[synchronous serial line]] [[peripheral|interface]] for the [[UNIBUS]]. It was double-[[buffer]]ed, and used [[programmed I/O]] (with separate receive and transmit [[interrupt]]s) to transfer data, in either [[half-duplex]] or [[full-duplex]], at [[baud rate]]s up to 50K bits/second; [[parity]] was supported for error detection. | + | The '''DP11-A Synchronous Line Interface''' is the earliest [[synchronous serial line]] [[peripheral|interface]] for the [[UNIBUS]]. It was double-[[buffer]]ed, and used [[programmed I/O]] (with separate receive and transmit [[interrupt]]s) to transfer data, in either [[half-duplex]] or [[full-duplex]], at [[baud rate]]s up to 50K bits/second; [[parity]] was supported for error detection. |

It was intended to interface to Bell 201, 301 and 303 series [[modem]]s. The [[character]] length (6, 7 or 8 [[bit]]s), and the [[sync character]], were selectable under program control, as were idling (sending the sync character), as well as the modem control leads; the DP11-A could also be set to discard incoming sync characters. | It was intended to interface to Bell 201, 301 and 303 series [[modem]]s. The [[character]] length (6, 7 or 8 [[bit]]s), and the [[sync character]], were selectable under program control, as were idling (sending the sync character), as well as the modem control leads; the DP11-A could also be set to discard incoming sync characters. | ||

| Line 25: | Line 25: | ||

|} | |} | ||

| − | The two SYNC registers | + | The two SYNC registers overlay the buffer registers; access to them is gained via byte UNIBUS operations to odd addresses. |

The [[address]]es shown are for the first DP11-A in a system; additional ones are normally set to be at 774760, 774750, etc to 774400. | The [[address]]es shown are for the first DP11-A in a system; additional ones are normally set to be at 774760, 774750, etc to 774400. | ||

| Line 105: | Line 105: | ||

Power comes in on a single-width stub card in the A3 slot (as is canonical in the [[PDP-11/20]] generation of [[PDP-11]]s). | Power comes in on a single-width stub card in the A3 slot (as is canonical in the [[PDP-11/20]] generation of [[PDP-11]]s). | ||

| − | [[Category:UNIBUS | + | ==Further reading== |

| + | |||

| + | * ''DP11 Synchronous Communication Interface Engineering Drawings'' (not online) | ||

| + | |||

| + | ==External links== | ||

| + | |||

| + | * [http://www.bitsavers.org/www.computer.museum.uq.edu.au/pdf/DEC-11-HDPAA-C-D%20DP11-A%20Synchronous%20Line%20Interface%20Manual.pdf DP11-A synchronous line interface manual] (DEC-11-HDPAA-C-D) | ||

| + | |||

| + | [[Category: UNIBUS Synchronous Serial Interfaces]] | ||

Latest revision as of 02:17, 18 February 2023

The DP11-A Synchronous Line Interface is the earliest synchronous serial line interface for the UNIBUS. It was double-buffered, and used programmed I/O (with separate receive and transmit interrupts) to transfer data, in either half-duplex or full-duplex, at baud rates up to 50K bits/second; parity was supported for error detection.

It was intended to interface to Bell 201, 301 and 303 series modems. The character length (6, 7 or 8 bits), and the sync character, were selectable under program control, as were idling (sending the sync character), as well as the modem control leads; the DP11-A could also be set to discard incoming sync characters.

Options allowed extending the character length to 10, 11 or 12 bits, and use of an internal clock.

It was constructed from a number of smaller FLIP CHIPs, along with a larger board, which were installed in a custom 4-slot backplane system unit. It used one of the DF11 Communications Line Adapters to interface to the modem.

Contents

Registers

| Register | Abbreviation | Address |

|---|---|---|

| Receiver Control and Status Register | DPRCSR | 774770 |

| Receiver Buffer Register | DPRBUF | 774772 |

| Sync Register | DPSYNC | 774773 |

| Additional Sync Register | DPASYNC | 774777 |

| Transmitter Control and Status Register | DPXCSR | 774774 |

| Transmitter Buffer Register | DPXBUF | 774776 |

The two SYNC registers overlay the buffer registers; access to them is gained via byte UNIBUS operations to odd addresses.

The addresses shown are for the first DP11-A in a system; additional ones are normally set to be at 774760, 774750, etc to 774400.

774770: Receiver Control and Status Register (DPRCSR)

| Unused | CPAR | RACT | BPCH | RDN | RDIE | Unused | MRCV | MAINT | HLFD | STRS | |||||

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

- CPAR - Character Parity; parity of last character in the receive buffer

- RACT - Receiver Active; set after two consecutive sync characters

- BPCH - Bits per Character, selects between 6-8, 10-12 bits per character

- RDN - Receive Done Flag; set when the receive buffer contains an assembled character

- RDIE - Receive Interrupt Enable; allows an input interrupt when Receive Done Flag is set

- MRCV - Miscellaneous Receive; monitor any non-standard modem status

- MAINT -Maintenance Mode; connect Transmitter output to Receiver input, CTS simulation

- HLFD - Half Duplex; RTS on inhibits Receive logic

- STRS - Strip Sync; sync characters following Receive Active are discarded

774774: Transmitter Control and Status Register (DPXCSR)

| CARRF | RXOF | RING | MRDY | CARR | CTS | RTS | Unused | XDN | XDIE | XSIE | Unused | MXMT | Unused | IDLS | TRDY |

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

- CARRF - Carrier Flag; set when modem's Carrier lead goes from On to Off

- RXOF - Receiver Overrun Flag; receiver buffer not read before end of next character

- RING - Ring Flag; indicates a Ring signal from the modem

- MRDY - Modem Ready; current state of modem Data Set Ready lead

- CARR - Carrier; current state of modem Carrier lead

- CTS - Clear to Send; current state of mode CTS lead

- RTS - Request to Send; set when transmit buffer is loaded, or if Idle Sync is set

- XDN - Transmit Done Flag; set when output character transmission has started

- XDIE - Transmit Done Interrupt Enable; allows a transmit interrupt when Transmit Done Flag is set

- XSIE - Transmit Status Interrupt Enable; allows a transmit interrupt when any flag bit is set

- MXMT - Miscellaneous Transmit; control any non-standard modem status

- IDLS - Idle Sync; allows transmission from the sync buffer

- TRDY - Terminal Ready; controls connection of data communication gear to communication channel

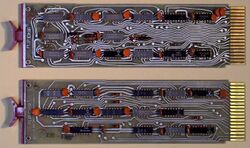

Implementation

The modules are:

- G8000 - +8V Filter

- M105 - UNIBUS Address Selector Module

- M239 - Divide by 16 Module (optional)

- M405 - Clock Module (optional)

- M594 - EIA Level Converter Module

- M7820 - Interrupt Control

- M7065 - Receiver Module (one mandatory, two optional)

- M7075 - Transmitter Module (ditto)

- M7223 - Control Module

The M7223 is a quad card; the others are all single. (Of those, the M105, M7820, M7065 and M7075 are extended length; the M239 and M405 are standard length.)

The M594 can be substituted with other adapter cards from the DF11 series; in particular, the M595 is used with the Bell 303 series modem.

Board locations (as seen from the board insertion side of the backplane, not the wire-wrap pin side, as is common in DEC documentation) are:

| Connector | ||||||

|---|---|---|---|---|---|---|

| Slot | A | B | C | D | E | F |

| 1 | UNIBUS In | M7223 | ||||

| 2 | G8000 Filter | M105 | M7820 | M405 | M239 | |

| 3 | Power | M7075 | M7065 | M7075 | M7065 | |

| 4 | UNIBUS Out | Modem connector | Level Converter | |||

Power comes in on a single-width stub card in the A3 slot (as is canonical in the PDP-11/20 generation of PDP-11s).

Further reading

- DP11 Synchronous Communication Interface Engineering Drawings (not online)

External links

- DP11-A synchronous line interface manual (DEC-11-HDPAA-C-D)