Difference between revisions of "MSV11-P MOS Random-Access Memory"

(+image) |

m (→Further reading: +Differences Between MSVI1-L and MSV11-P Memories) |

||

| (2 intermediate revisions by the same user not shown) | |||

| Line 3: | Line 3: | ||

The '''MSV11-P''' (M8067) is a [[DEC card form factor|quad]]-height [[QBUS]] [[Dynamic RAM|DRAM]] [[main memory]] card. The MSV11-PL (M8067-Lx) holds 512 KBytes when fully populated with 64K DRAMs [[integrated circuit|chips]], the MSV11-PK (M8067-Kx) is half-populated (the only partially-filled configuration allowed) and holds 256 Kbytes. (The 'x' in the board identifier is a capital letter which identifies the manufacturer of the DRAM chips.) | The '''MSV11-P''' (M8067) is a [[DEC card form factor|quad]]-height [[QBUS]] [[Dynamic RAM|DRAM]] [[main memory]] card. The MSV11-PL (M8067-Lx) holds 512 KBytes when fully populated with 64K DRAMs [[integrated circuit|chips]], the MSV11-PK (M8067-Kx) is half-populated (the only partially-filled configuration allowed) and holds 256 Kbytes. (The 'x' in the board identifier is a capital letter which identifies the manufacturer of the DRAM chips.) | ||

| − | The memory is arranged as 2 banks, each 16 data bits (1 [[PDP-11]] [[word]]) wide, with 2 additional bits for [[parity]] (1 per [[byte]]). It can be configured as either a [[QBUS#Variable address size|Q18]] card, or a Q22 card; the - | + | The memory is arranged as 2 banks, each 16 data bits (1 [[PDP-11]] [[word]]) wide, with 2 additional bits for [[parity]] (1 per [[byte]]). It can be configured as either a [[QBUS#Variable address size|Q18]] card, or a Q22 card; the -PL ''must'' be configured as a Q22 card due to its size. It can also be configured for use either in a [[QBUS#Backplanes|Q/CD backplane]] or a [[QBUS#Backplanes|Q/Q backplane]]. <!--; it reportedly supports QBUS block mode-->. |

==Configuration== | ==Configuration== | ||

| Line 78: | Line 78: | ||

==Further reading== | ==Further reading== | ||

| − | * ''MSV11-P | + | * ''Differences Between MSVI1-L and MSV11-P Memories'', [[MicroNote]] #111 |

| − | |||

| − | + | ==External links== | |

| + | |||

| + | * [http://bitsavers.org/pdf/dec/qbus/EK-MSV0P-UG-001_MSV11P_Aug81.pdf MSV11-P User Guide] (EK-MSV0P-UG-001) | ||

| + | * [https://manx-docs.org/collections/hcps/msv11p.pdf MSV11-P Field Maintenance Print Set] (MP01239) | ||

[[Category: QBUS Memories]] | [[Category: QBUS Memories]] | ||

Latest revision as of 21:36, 25 July 2024

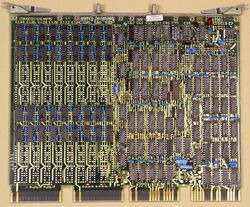

The MSV11-P (M8067) is a quad-height QBUS DRAM main memory card. The MSV11-PL (M8067-Lx) holds 512 KBytes when fully populated with 64K DRAMs chips, the MSV11-PK (M8067-Kx) is half-populated (the only partially-filled configuration allowed) and holds 256 Kbytes. (The 'x' in the board identifier is a capital letter which identifies the manufacturer of the DRAM chips.)

The memory is arranged as 2 banks, each 16 data bits (1 PDP-11 word) wide, with 2 additional bits for parity (1 per byte). It can be configured as either a Q18 card, or a Q22 card; the -PL must be configured as a Q22 card due to its size. It can also be configured for use either in a Q/CD backplane or a Q/Q backplane. .

Configuration

The card is configured by jumpers on wire-wrap posts; it is possible to set:

- the starting address;

- the size (256KB or 512KB);

- the CSR address;

- enable wrong parity.

Further reading

- Differences Between MSVI1-L and MSV11-P Memories, MicroNote #111

External links

- MSV11-P User Guide (EK-MSV0P-UG-001)

- MSV11-P Field Maintenance Print Set (MP01239)