Difference between revisions of "MMV11-A QBUS core memory"

m (→Further reading: +Core Memory in 11/03-L Backplane) |

m (→See also: typo) |

||

| Line 18: | Line 18: | ||

==See also== | ==See also== | ||

| − | * [[QBUS memories] | + | * [[QBUS memories]] |

==Further reading== | ==Further reading== | ||

Latest revision as of 17:32, 27 July 2024

MMV11-A is a core main memory module for the QBUS - the only core main memory from DEC for the QBUS.

An MMV11-A holds 8K bytes; it has an access time of 425 nsec, and a cycle time of 1.15 μsec.

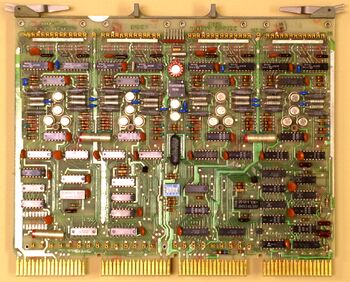

An MMV11-A was composed of two quad-sized boards, one piggy-backed on the other, and the pair taking only a single backplane slot (electrically):

- An H223 daughter-board containing the cores

- A G653 mother-board containing most of the electronics, and the contact fingers for plugging into the backplane.

The MMV11-A did not use a custom backplane; it plugged into a standard Q/Q backplane. However, it did use QBUS signals on the right-hand C/D connectors, so it could not be plugged into a Q/CD backplane.

The pair was 'thick' enough that a normal board cannot be plugged into the next slot. DEC documentation indicates that if there are devices 'behind' the MMV11-A on the bus, the bus grant lines (BIAK and BDMG) must be jumpered on the backplane in that slot.

The MMV11-A was a Q16 card, so could only be used on systems with a maximum of 64KB of memory.

See also

Further reading

- Core Memory in 11/03-L Backplane, MicroNote #036

External links

- LSI-11, PDP-11/03 user's manual (EK-LSI11-TM-002) - the MMV11-A is covered in Section 4.3 (pp. 52-62 of the PDF) and Chapter 8 (pp. 111-112 of the PDF)

- microcomputer processor handbook - the MMV11-A is covered on Chapter 12, pp. 367-384 (pp. 377-394 of the PDF)

- Microcomputer Handbook (1976-77) - the MMV11-A is covered on pp. 4-16—4-30 and 5-11—5-14 (pp. 99-113 and 164-167 of the PDF)

- ET-LSI-11 Field Maintenance Print Set (MP00706) - the MMV11-A covered on pp. 170-177