Difference between revisions of "DL11 asynchronous serial line interface"

m (→Versions: typo) |

m (Add links; fmt) |

||

| (20 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

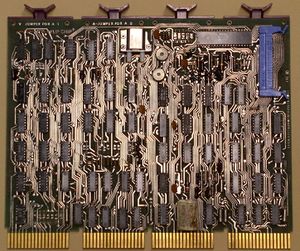

| − | + | [[Image:M7800DL11E.jpg|300px|thumb|right|DL11-E card]] | |

| − | + | The '''DL11 asynchronous serial line interface''' card (M7800) was a [[UNIBUS]] [[peripheral]] for the [[PDP-11]] series of computers which provided a single [[asynchronous serial line]]. It was a [[DEC card form factor|quad]] format card, and used an [[Small Peripheral Controller|SPC]] slot. | |

| − | + | It provided both [[20mA current loop serial line interface|20mA]] and (in some versions) [[EIA RS-232 serial line interface|EIA RS-232]] connectivity at speeds of 110 to 9600 [[baud rate|baud]] (the range depended on the version); the DL11-E version also provided full [[modem]] control. Line connection was via a 40-pin [[Berg connector]] header on the top edge of the card, using the standard [[DEC asynchronous serial line pinout]]; [[transistor-transistor logic|TTL]]-level signals were also present on this connector. | |

| − | The DL11 has 2 registers for the receive side (one Control and Status Register - CSR - and one data buffer register), and similarly, two for the transmit side. Each DL11 has two interrupt | + | It was a functionally identical single-board replacement for the [[KL11 asynchronous serial line interface]], which consisted of a dual card, along with two standard single card [[FLIP CHIP]]s. The DL11 also made use of the then-new [[Universal Asynchronous Receiver/Transmitter|UART]] [[MSI]] [[integrated circuit|chip]]. |

| + | |||

| + | The [[TU58]] tape drive is connected to a DL11-type device, so the device [[address]], etc for TU58's are as for DL11's - the [[register]] addresses and [[interrupt vector]]s are those given below for the 'first' DL11 (DL11 #1). | ||

| + | |||

| + | ==Connection== | ||

| + | |||

| + | Selecting between current-loop and EIA interface inputs is done by loopbacks on the Berg connector, called "interlock". | ||

| + | |||

| + | * The actual input is TTL on pin 'E' (labelled "Serial Input TTL" and "Interlock In") | ||

| + | * The current loop receiver has input on 'K' and 'S', output on 'H' ("20 mA Interlock Out") | ||

| + | * The current loop output is on 'AA' and 'KK' | ||

| + | * (optional) EIA level receiver has input on 'J', output on 'M' ("EIA Interlock Out") | ||

| + | * (optional) EIA output is on 'F' | ||

| + | |||

| + | So, for current loop, we join H to E (and connect K, S, AA, KK to the communicating system). For EIA we join M to E (and connect at least J, F to the other system.) These configurations are normally done in the cable; see the DL11 manual, tables 3-3 to 3-6. | ||

| + | |||

| + | ==Programming interface== | ||

| + | |||

| + | The DL11 has 2 device registers for the receive side (one Control and Status Register - CSR - and one data [[buffer]] register), and similarly, two for the transmit side. Each DL11 has two interrupt vectors - again, one receive, and one transmit. | ||

| + | |||

| + | For the PDP-11 main console (which is always a KL11/DL11 compatible device), the 'zeroth' DL11, the standard is that 0777560 is the base address (so the receiver registers are 0777560-2, and the transmitter are 0777564-6), and 060 is the base vector. | ||

| + | |||

| + | The first DL11 after the console is always assigned the address 0776500, and vector 0300. Additional DL11's are assigned addresses and vectors immediately following, for DL11's #1-#16 (i.e. 0776500-676 and 0300-0476). | ||

==Configuration== | ==Configuration== | ||

| − | The bus address, interrupt vector, and line parameters (parity, stop | + | The bus address, interrupt vector, and line parameters ([[parity]], number of stop and data bits) were selected by soldered [[jumper]]s; the baud rate was set by a combination of a replaceable crystal (several different ones were standard), and a pair of 10-position dial selectors (one for transmit, one for receive) which selected a rate: |

{| class="wikitable" | {| class="wikitable" | ||

| Line 23: | Line 45: | ||

|} | |} | ||

| − | The address and vector jumpers specify the base of the bus | + | (The 9th and 10th dial selector positions selected external [[clock]] inputs, not divisions of the crystal.) |

| + | |||

| + | The address and vector jumpers specify the base of the register bus addresses, and vectors, in binary. On the DL11, it is only possible to set the base of the entire group of 4 registers; the transmit and receive register groups cannot be moved around independently. Similarly for the vector, only the base of the pair of vectors can be configured; the receive (at B) and transmit (at B+4) are paired in the hardware. | ||

The simple rule on the DL11 is that vector jumpers are the inverse of address jumpers: for the vector, jumpers are 'in' for '1', and for the address, they are 'in' for '0'. (This inversion can be a memory jogger - 'Oh, the DL11, that blasted interface where the jumper sense is inverted between address and vector!' Then one only has to look up one of the two.) | The simple rule on the DL11 is that vector jumpers are the inverse of address jumpers: for the vector, jumpers are 'in' for '1', and for the address, they are 'in' for '0'. (This inversion can be a memory jogger - 'Oh, the DL11, that blasted interface where the jumper sense is inverted between address and vector!' Then one only has to look up one of the two.) | ||

| − | + | Address jumper A3 is the 3rd bit of the address, i.e. the 010 bit, the lowest one that is configurable (the device is a block of 8 bytes, from xxxxx0 to xxxxx7, so it is not possible to set any of the low 3 bits in the base address, they must be 0), and A10 is the highest bit which can be changed. V3 through V8 perform a similar function for the vectors. | |

The following table shows the bits which are affected when the jumper is '''''in'''''. | The following table shows the bits which are affected when the jumper is '''''in'''''. | ||

| Line 53: | Line 77: | ||

===Sample configurations=== | ===Sample configurations=== | ||

| − | + | The following table gives the jumper configuration for the two most common DL11 configurations: | |

| − | + | * main console (address 0777560, vector 060) | |

| − | + | * 'first' DL11 - often a TU58, now (address 0776500, vector 0300) | |

{| class="wikitable" | {| class="wikitable" | ||

| Line 75: | Line 99: | ||

|- | |- | ||

| A10 || 02000 ||Out || Out | | A10 || 02000 ||Out || Out | ||

| + | |- | ||

| + | | colspan="3" | | ||

|- | |- | ||

| V3 || 010 || Out || Out | | V3 || 010 || Out || Out | ||

| Line 95: | Line 121: | ||

The -A and -C versions (board M7800-YA on at least one of these) were 20mA interface '''only''', and omitted the components necessary for the EIA interface. | The -A and -C versions (board M7800-YA on at least one of these) were 20mA interface '''only''', and omitted the components necessary for the EIA interface. | ||

| − | The -A and -B apparently did not provide full baud rate selection and selectable data coding (they were restricted to 8-bit data, no parity, and 1 or 2 stop bits); they also could not provide 'split' speeds (differing baud rates on transmit and receive). Apparently, these versions had more limited address selection capability; they could only be configured to | + | The -A and -B apparently did not provide full baud rate selection and selectable data coding (they were restricted to 8-bit data, no parity, and 1 or 2 stop bits); they also could not provide 'split' speeds (differing baud rates on transmit and receive). Apparently, these versions had more limited address selection capability; they could only be configured to 0776XX0, where XX ranged from 050 to 067. |

Only the -C through -E could be ordered with the 4th (9600-baud capable) crystal (it is not known whether the earlier ones would work if this crystal were inserted). Only the -E provided full modem control. | Only the -C through -E could be ordered with the 4th (9600-baud capable) crystal (it is not known whether the earlier ones would work if this crystal were inserted). Only the -E provided full modem control. | ||

| − | The -A and -C versions are easy to identify visually; they are both missing | + | The -A and -C versions are easy to identify visually; they are both missing a large number of components (five 14-pin chips including 1488, 1489 which are RS-232 receiver and driver chips). |

| − | a large number of components. How to tell the others apart (if, indeed, there | + | |

| − | is any difference between the -D and -E) is not yet documented. | + | How to tell the others apart (if, indeed, there is any difference between the -D and -E) is not yet documented. |

| + | |||

| + | ==See also== | ||

| + | |||

| + | * [[DL11-W serial line unit/real-time clock option]] | ||

| + | |||

| + | ==External links== | ||

| + | |||

| + | * [http://www.bitsavers.org/pdf/dec/unibus/EK-DL11-OP-001_Sep76.pdf DL11 asynchronous line interface user's manual] (EK-DL11-OP-001) | ||

| + | * [http://www.bitsavers.org/pdf/dec/unibus/EK-DL11-TM-003_DL11_Asynchronous_Line_Interface_Manual_Sep75.pdf DL11 asynchronous line interface manual] (EK-DL11-TM-003) - technical manual | ||

| + | * [http://www.bitsavers.org/pdf/dec/unibus/DL11_EngrDrws.pdf DL11 asynchronous line interface engineering drawings] - originals | ||

| + | * [http://www.bitsavers.org/pdf/dec/unibus/DL11_schem_Mar78.pdf DL11 asynchronous line interface engineering drawings] - redrawn | ||

| + | * [https://chdickman.com/pdp11/Notes/DL11.shtml Notes: DEC DL11] | ||

| − | + | [[Category: UNIBUS Asynchronous Serial Interfaces]] | |

Latest revision as of 09:23, 27 September 2024

The DL11 asynchronous serial line interface card (M7800) was a UNIBUS peripheral for the PDP-11 series of computers which provided a single asynchronous serial line. It was a quad format card, and used an SPC slot.

It provided both 20mA and (in some versions) EIA RS-232 connectivity at speeds of 110 to 9600 baud (the range depended on the version); the DL11-E version also provided full modem control. Line connection was via a 40-pin Berg connector header on the top edge of the card, using the standard DEC asynchronous serial line pinout; TTL-level signals were also present on this connector.

It was a functionally identical single-board replacement for the KL11 asynchronous serial line interface, which consisted of a dual card, along with two standard single card FLIP CHIPs. The DL11 also made use of the then-new UART MSI chip.

The TU58 tape drive is connected to a DL11-type device, so the device address, etc for TU58's are as for DL11's - the register addresses and interrupt vectors are those given below for the 'first' DL11 (DL11 #1).

Contents

Connection

Selecting between current-loop and EIA interface inputs is done by loopbacks on the Berg connector, called "interlock".

- The actual input is TTL on pin 'E' (labelled "Serial Input TTL" and "Interlock In")

- The current loop receiver has input on 'K' and 'S', output on 'H' ("20 mA Interlock Out")

- The current loop output is on 'AA' and 'KK'

- (optional) EIA level receiver has input on 'J', output on 'M' ("EIA Interlock Out")

- (optional) EIA output is on 'F'

So, for current loop, we join H to E (and connect K, S, AA, KK to the communicating system). For EIA we join M to E (and connect at least J, F to the other system.) These configurations are normally done in the cable; see the DL11 manual, tables 3-3 to 3-6.

Programming interface

The DL11 has 2 device registers for the receive side (one Control and Status Register - CSR - and one data buffer register), and similarly, two for the transmit side. Each DL11 has two interrupt vectors - again, one receive, and one transmit.

For the PDP-11 main console (which is always a KL11/DL11 compatible device), the 'zeroth' DL11, the standard is that 0777560 is the base address (so the receiver registers are 0777560-2, and the transmitter are 0777564-6), and 060 is the base vector.

The first DL11 after the console is always assigned the address 0776500, and vector 0300. Additional DL11's are assigned addresses and vectors immediately following, for DL11's #1-#16 (i.e. 0776500-676 and 0300-0476).

Configuration

The bus address, interrupt vector, and line parameters (parity, number of stop and data bits) were selected by soldered jumpers; the baud rate was set by a combination of a replaceable crystal (several different ones were standard), and a pair of 10-position dial selectors (one for transmit, one for receive) which selected a rate:

| Crystal Speed | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|---|---|---|---|---|---|---|---|---|

| 884.8 KHz | 35.7 | 55 | 110 | 220 | 440 | 880 | 1320 | 1760 |

| 1.033 MHz | 44.8 | 67.3 | 134.5 | 269 | 538 | 1076 | 1614 | 2152 |

| 1.152 MHz | 50 | 75 | 150 | 300 | 600 | 1200 | 1800 | 2400 |

| 4.608 MHz | 200 | 300 | 600 | 1200 | 2400 | 4800 | 7200 | 9600 |

(The 9th and 10th dial selector positions selected external clock inputs, not divisions of the crystal.)

The address and vector jumpers specify the base of the register bus addresses, and vectors, in binary. On the DL11, it is only possible to set the base of the entire group of 4 registers; the transmit and receive register groups cannot be moved around independently. Similarly for the vector, only the base of the pair of vectors can be configured; the receive (at B) and transmit (at B+4) are paired in the hardware.

The simple rule on the DL11 is that vector jumpers are the inverse of address jumpers: for the vector, jumpers are 'in' for '1', and for the address, they are 'in' for '0'. (This inversion can be a memory jogger - 'Oh, the DL11, that blasted interface where the jumper sense is inverted between address and vector!' Then one only has to look up one of the two.)

Address jumper A3 is the 3rd bit of the address, i.e. the 010 bit, the lowest one that is configurable (the device is a block of 8 bytes, from xxxxx0 to xxxxx7, so it is not possible to set any of the low 3 bits in the base address, they must be 0), and A10 is the highest bit which can be changed. V3 through V8 perform a similar function for the vectors.

The following table shows the bits which are affected when the jumper is in.

| Address Jumper | Address Bit | Vector Jumper | Vector bit |

|---|---|---|---|

| A3 | -010 | V3 | +010 |

| A4 | -020 | V4 | +020 |

| A5 | -040 | V5 | +040 |

| A6 | -0100 | V6 | +0100 |

| A7 | -0200 | V7 | +0200 |

| A8 | -0400 | V8 | +0400 |

| A9 | -01000 | ||

| A10 | -02000 |

Sample configurations

The following table gives the jumper configuration for the two most common DL11 configurations:

- main console (address 0777560, vector 060)

- 'first' DL11 - often a TU58, now (address 0776500, vector 0300)

| Jumper | Bit | Console | First DL11 |

|---|---|---|---|

| A3 | 010 | In | In |

| A4 | 020 | Out | In |

| A5 | 040 | Out | In |

| A6 | 0100 | Out | Out |

| A7 | 0200 | In | In |

| A8 | 0400 | Out | Out |

| A9 | 01000 | Out | In |

| A10 | 02000 | Out | Out |

| V3 | 010 | Out | Out |

| V4 | 020 | In | Out |

| V5 | 040 | In | Out |

| V6 | 0100 | Out | In |

| V7 | 0200 | Out | In |

| V8 | 0400 | Out | Out |

Versions

The DL11 came in 5 versions, -A through -E.

The -A and -C versions (board M7800-YA on at least one of these) were 20mA interface only, and omitted the components necessary for the EIA interface.

The -A and -B apparently did not provide full baud rate selection and selectable data coding (they were restricted to 8-bit data, no parity, and 1 or 2 stop bits); they also could not provide 'split' speeds (differing baud rates on transmit and receive). Apparently, these versions had more limited address selection capability; they could only be configured to 0776XX0, where XX ranged from 050 to 067.

Only the -C through -E could be ordered with the 4th (9600-baud capable) crystal (it is not known whether the earlier ones would work if this crystal were inserted). Only the -E provided full modem control.

The -A and -C versions are easy to identify visually; they are both missing a large number of components (five 14-pin chips including 1488, 1489 which are RS-232 receiver and driver chips).

How to tell the others apart (if, indeed, there is any difference between the -D and -E) is not yet documented.

See also

External links

- DL11 asynchronous line interface user's manual (EK-DL11-OP-001)

- DL11 asynchronous line interface manual (EK-DL11-TM-003) - technical manual

- DL11 asynchronous line interface engineering drawings - originals

- DL11 asynchronous line interface engineering drawings - redrawn

- Notes: DEC DL11