Difference between revisions of "National Semiconductor NS23C QBUS memory"

m (→246KB to 1M Upgrade: typp 246->256) |

m (Avoid dab) |

||

| (15 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

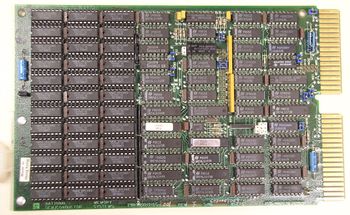

| − | The '''National Semiconductor NS23C''' is a [[QBUS]] memory card in dual QBUS card-size format, with a maximum capacity of 256 Kbyte (using 64Kx1 [[ | + | [[Image:NS23C.jpg|350px|right|thumb|NS23C card]] |

| + | |||

| + | The '''National Semiconductor NS23C''' is a [[QBUS]] [[main memory]] card in [[DEC card form factor|dual]] QBUS card-size format, with a maximum capacity of 256 Kbyte (using 64Kx1 [[Dynamic RAM|DRAMs]]), or 1 Mbyte (un-documented, using 256Kx1 DRAMs). (The card may be configured to provide less memory than is physically present.) | ||

| + | |||

| + | It provides byte [[parity]], and supports QBUS Block Mode. (Note that block mode '''must''' be disabled on older [[LSI-11]] systems, including the LSI-11/2.) Internal or external [[memory refresh]] may be used | ||

| + | |||

| + | ==Identification== | ||

| + | |||

| + | Unlike the [[National Semiconductor NS23M QBUS memory|NS23M]], the NS23C [[printed circuit board]] does contain identification which indicates that it is an NS23C; in addition, the PCB says "PWB 551010105-002" on the solder side, and "PWA 980010105" on the component side. | ||

==256KB to 1M Upgrade== | ==256KB to 1M Upgrade== | ||

| − | It is very easy to upgrade these | + | It is very easy to upgrade these cards from 256KB to 1MB, as it has all the necessary traces, jumpers, etc for this capability built into the card - even though the NS23C documentation says nothing about this capability! |

| + | |||

| + | Looking at the prints, the memory [[integrated circuit|chips]] have all 9 [[address]] lines wired (unlike the very similar NS23M card), and there are several jumpers that adapt the card to 1MB operation. The chips are all in [[chip socket]]s, so pulling the 64Kx1's and replacing them with 256Kx1's is easy. | ||

| + | |||

| + | There are three 'jumpers' one has to remove/move; alas, they are traces in the PCB on the top surface, although there are jumper pins there - as built, there is a trace running between the two pins - so those traces have to be cut. | ||

| − | + | The first two 'jumpers' one has to remove are W23 and W24 (right next to the other memory size jumpers), which allow one to increase the maximum memory size to 1MB. | |

| − | + | The other 'jumper' one has to do is to move the 'jumper' from W40 to W41; this moves the pickup point for the 'RS0' signal, which indicates which bank of chips (there are 2x18 banks, i.e. 16 data, and separate byte parity) to activate, from address line 17 to 19. | |

| − | + | ==Control and Status Register== | |

| − | The | + | The NS23C has an optional Control and Status Register, which may be configured, and can be placed at one of eight locations. The layout is: |

| + | {{16bit-header}} | ||

| + | | Parity Error || Extended CSR Enable || colspan=2 | Unused || colspan=3 | A17-A15 || colspan=4 | A21-A18 or<br> A14-A11 || colspan=2 | Unused || Write Wrong Parity || Unused || Parity Error Enable | ||

| + | {{16bit-bitout}} | ||

| − | == Fault Isolation== | + | |

| + | ==Configuration== | ||

| + | |||

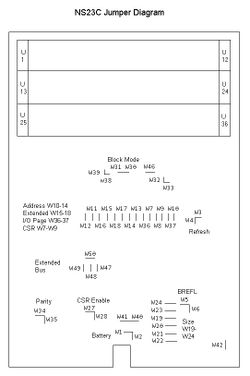

| + | [[Image:NS23C Jumpers.jpg|250px|thumb|right|NS23C configuration jumpers location diagram]] | ||

| + | |||

| + | Since the 1 Mbyte option is un-documented, here is updated information on how to configure the board. | ||

| + | |||

| + | ===Size=== | ||

| + | |||

| + | First, the low-order size bits, which are the same as the un-modified board: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! rowspan="2" style="text-align:center;" | Size<br>(Decimal) !! rowspan="2" style="text-align:center;" | Size<br>(Octal) !! colspan="4" style="text-align:center;" | Jumpers | ||

| + | |- | ||

| + | | W22 || W21 || W20 || W19 | ||

| + | |- | ||

| + | | 16KB || 000000 || I || I || I || I | ||

| + | |- | ||

| + | | 32KB || 010000 || I || I || I || R | ||

| + | |- | ||

| + | | 48KB || 020000 || I || I || R || I | ||

| + | |- | ||

| + | | 64KB || 030000 || I || I || R || R | ||

| + | |- | ||

| + | | 80KB || 040000 || I || R || I || I | ||

| + | |- | ||

| + | | 96KB || 050000 || I || R || I || R | ||

| + | |- | ||

| + | | 112KB || 060000 || I || R || R || I | ||

| + | |- | ||

| + | | 128KB || 400000 || I || R || R || R | ||

| + | |- | ||

| + | | 144KB || 440000 || R || I || I || I | ||

| + | |- | ||

| + | | 160KB || 500000 || R || I || I || R | ||

| + | |- | ||

| + | | 176KB || 540000 || R || I || R || I | ||

| + | |- | ||

| + | | 192KB || 600000 || R || I || R || R | ||

| + | |- | ||

| + | | 208KB || 640000 || R || R || I || I | ||

| + | |- | ||

| + | | 224KB || 700000 || R || R || I || R | ||

| + | |- | ||

| + | | 240KB || 740000 || R || R || R || I | ||

| + | |- | ||

| + | | 256KB || 1000000 || R || R || R || R | ||

| + | |} | ||

| + | |||

| + | and now the high-order size bits, which were not previously documented: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! rowspan="2" style="text-align:center;" | Size<br>(Decimal) !! rowspan="2" style="text-align:center;" | Size<br>(Octal) !! colspan="2" style="text-align:center;" | Jumpers | ||

| + | |- | ||

| + | | W24 || W23 | ||

| + | |- | ||

| + | | 256KB || 1000000 || I || I | ||

| + | |- | ||

| + | | 512KB || 2000000 || I || R | ||

| + | |- | ||

| + | | 768KB || 3000000 || R || I | ||

| + | |- | ||

| + | | 1024KB || 4000000 || R || R | ||

| + | |} | ||

| + | |||

| + | ===Address=== | ||

| + | |||

| + | The starting address is also entirely the same as the un-modified board; first, the low-order starting address bits: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! rowspan="2" style="text-align:center;" | Starting<br>Address<br>(Decimal) !! rowspan="2" style="text-align:center;" | Starting<br>Address<br>(Octal) !! colspan="5" style="text-align:center;" | Jumpers | ||

| + | |- | ||

| + | | W10 || W11 || W12 || W13 || W14 | ||

| + | |- | ||

| + | | 0KB || 000000 || R || R || R || R || R | ||

| + | |- | ||

| + | | 8KB || 020000 || I || R || R || R || R | ||

| + | |- | ||

| + | | 16KB || 040000 || R || I || R || R || R | ||

| + | |- | ||

| + | | 24KB || 060000 || I || I || R || R || R | ||

| + | |- | ||

| + | | 32KB || 100000 || R || R || I || R || R | ||

| + | |- | ||

| + | | 40KB || 120000 || I || R || I || R || R | ||

| + | |- | ||

| + | | 48KB || 1400000 || R || I || I || R || R | ||

| + | |- | ||

| + | | 56KB || 160000 || I || I || I || R || R | ||

| + | |- | ||

| + | | 64KB || 200000 || R || R || R || I || R | ||

| + | |- | ||

| + | | 72KB || 220000 || I || R || R || I || R | ||

| + | |- | ||

| + | | 80KB || 240000 || R || I || R || I || R | ||

| + | |- | ||

| + | | 88KB || 260000 || I || I || R || I || R | ||

| + | |- | ||

| + | | 96KB || 300000 || R || R || I || I || R | ||

| + | |- | ||

| + | | 104KB || 320000 || I || R || I || I || R | ||

| + | |- | ||

| + | | 112KB || 340000 || R || I || I || I || R | ||

| + | |- | ||

| + | | 120KB || 360000 || I || I || I || I || R | ||

| + | |- | ||

| + | | 128KB || 400000 || R || R || R || R || I | ||

| + | |- | ||

| + | | 136KB || 420000 || I || R || R || R || I | ||

| + | |- | ||

| + | | 144KB || 440000 || R || I || R || R || I | ||

| + | |- | ||

| + | | 152KB || 460000 || I || I || R || R || I | ||

| + | |- | ||

| + | | 160KB || 500000 || R || R || I || R || I | ||

| + | |- | ||

| + | | 168KB || 520000 || I || R || I || R || I | ||

| + | |- | ||

| + | | 176KB || 540000 || R || I || I || R || I | ||

| + | |- | ||

| + | | 184KB || 560000 || I || I || I || R || I | ||

| + | |- | ||

| + | | 192KB || 600000 || R || R || R || I || I | ||

| + | |- | ||

| + | | 200KB || 620000 || I || R || R || I || I | ||

| + | |- | ||

| + | | 208KB || 640000 || R || I || R || I || I | ||

| + | |- | ||

| + | | 216KB || 660000 || I || I || R || I || I | ||

| + | |- | ||

| + | | 224KB || 700000 || R || R || I || I || I | ||

| + | |- | ||

| + | | 232KB || 720000 || I || R || I || I || I | ||

| + | |- | ||

| + | | 240KB || 740000 || R || I || I || I || I | ||

| + | |- | ||

| + | | 248KB || 760000 || I || I || I || I || I | ||

| + | |} | ||

| + | |||

| + | and then the high-order starting address bits: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! rowspan="2" style="text-align:center;" | Starting<br>Address<br>(Decimal) !! rowspan="2" style="text-align:center;" | Starting<br>Address<br>(Octal) !! colspan="4" style="text-align:center;" | Jumpers | ||

| + | |- | ||

| + | | W15 || W16 || W17 || W18 | ||

| + | |- | ||

| + | | 0KB || 00000000 || R || R || R || R | ||

| + | |- | ||

| + | | 256KB || 01000000 || I || R || R || R | ||

| + | |- | ||

| + | | 512KB || 02000000 || R || I || R || R | ||

| + | |- | ||

| + | | 768KB || 03000000 || I || I || R || R | ||

| + | |- | ||

| + | | 1024KB || 04000000 || R || R || I || R | ||

| + | |- | ||

| + | | 1280KB || 05000000 || I || R || I || R | ||

| + | |- | ||

| + | | 1536KB || 06000000 || R || I || I || R | ||

| + | |- | ||

| + | | 1792KB || 07000000 || I || I || I || R | ||

| + | |- | ||

| + | | 2048KB || 10000000 || R || R || R || I | ||

| + | |- | ||

| + | | 2304KB || 11000000 || I || R || R || I | ||

| + | |- | ||

| + | | 2560KB || 12000000 || R || I || R || I | ||

| + | |- | ||

| + | | 2816KB || 13000000 || I || I || R || I | ||

| + | |- | ||

| + | | 3072KB || 14000000 || R || R || I || I | ||

| + | |- | ||

| + | | 3328KB || 15000000 || I || R || I || I | ||

| + | |- | ||

| + | | 3584KB || 16000000 || R || I || I || I | ||

| + | |- | ||

| + | | 3840KB || 17000000 || I || I || I || I | ||

| + | |} | ||

| + | |||

| + | ===Other=== | ||

| + | |||

| + | CSR Address: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! rowspan="2" style="text-align:center;" | Address !! colspan="3" style="text-align:center;" | Jumpers | ||

| + | |- | ||

| + | | W9 || W8 || W7 | ||

| + | |- | ||

| + | | 772100 || I || I || I | ||

| + | |- | ||

| + | | 772102 || R || I || I | ||

| + | |- | ||

| + | | 772104 || I || R || I | ||

| + | |- | ||

| + | | 772106 || R || R || I | ||

| + | |- | ||

| + | | 772110 || I || I || R | ||

| + | |- | ||

| + | | 772112 || R || I || R | ||

| + | |- | ||

| + | | 772114 || I || R || R | ||

| + | |- | ||

| + | | 772116 || R || R || R | ||

| + | |} | ||

| + | |||

| + | Extended QBUS address type: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! rowspan="2" style="text-align:center;" | Address Type !! colspan="4" style="text-align:center;" | Jumpers | ||

| + | |- | ||

| + | | W47 || W48 || W49 || W50 | ||

| + | |- | ||

| + | | 18-bit || R || R || R || R | ||

| + | |- | ||

| + | | 19-bit || I || R || R || R | ||

| + | |- | ||

| + | | 20-bit || I || I || R || R | ||

| + | |- | ||

| + | | 21-bit || I || I || R || I | ||

| + | |- | ||

| + | | 22-bit || I || I || I || I | ||

| + | |} | ||

| + | |||

| + | Other: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! rowspan="2" style="text-align:center;" | Jumper !! rowspan="2" style="text-align:center;" | Function !! colspan="2" style="text-align:center;" | Jumpers | ||

| + | |- | ||

| + | | In || Out | ||

| + | |- | ||

| + | | W1 || rowspan="2" | Battery backup || None || Use | ||

| + | |- | ||

| + | | W2 || Use || None | ||

| + | |- | ||

| + | | W3 || rowspan="4" | Refresh || Internal || External | ||

| + | |- | ||

| + | | W4 || External || Internal | ||

| + | |- | ||

| + | | W5 || BREF Inhibit || Non-Inhibit | ||

| + | |- | ||

| + | | W6 || Non-Inhibit || BREF Inhibit | ||

| + | |- | ||

| + | | W27 || rowspan="2" | CSR || Enable || Disable | ||

| + | |- | ||

| + | | W28 || Disable || Enable | ||

| + | |- | ||

| + | | W30 || rowspan="2" | Block Mode || Disable || Enable | ||

| + | |- | ||

| + | | W31 || Enable || Disable | ||

| + | |- | ||

| + | | W35 || Parity Enable || Disabled || Enabled | ||

| + | |- | ||

| + | | W36 || rowspan="2" | I/O Page || 1 KW || 2/4 KW | ||

| + | |- | ||

| + | | W37 || 1/2 KW || 4 KW | ||

| + | |} | ||

| + | |||

| + | All other jumpers are manufacturing-related; leave as they are. | ||

| + | |||

| + | ==Fault Isolation== | ||

The way the address logic works on the card is slightly odd; if the card is not on a 'natural' boundary [e.g. a 256KB boundary, if it's a 256KB card], the memory contents are scrambled; the low memory, in bus address terms, is at the top of the card, in chip terms, and the high memory, in bus terms, is at the bottom of the card. | The way the address logic works on the card is slightly odd; if the card is not on a 'natural' boundary [e.g. a 256KB boundary, if it's a 256KB card], the memory contents are scrambled; the low memory, in bus address terms, is at the top of the card, in chip terms, and the high memory, in bus terms, is at the bottom of the card. | ||

They did it that way because that's the most economical way to do it in logic/traces, etc but it's something one would have to remember when looking for a bad memory chip, if the card is set to an address which is not a multiple of its size. | They did it that way because that's the most economical way to do it in logic/traces, etc but it's something one would have to remember when looking for a bad memory chip, if the card is set to an address which is not a multiple of its size. | ||

| + | |||

| + | ===Chip Table=== | ||

| + | |||

| + | To aid fault isolation, here is a table which relates bit numbers in memory words to chip numbers: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! Bit !! Low Bank !! High Bank | ||

| + | |- | ||

| + | | 0 || U12 || U24 | ||

| + | |- | ||

| + | | 1 || U11 || U36 | ||

| + | |- | ||

| + | | 2 || U10 || U23 | ||

| + | |- | ||

| + | | 3 || U22 || U35 | ||

| + | |- | ||

| + | | 4 || U9 || U34 | ||

| + | |- | ||

| + | | 5 || U21 || U33 | ||

| + | |- | ||

| + | | 6 || U8 || U20 | ||

| + | |- | ||

| + | | 7 || U7 || U32 | ||

| + | |- | ||

| + | | 8 || U6 || U19 | ||

| + | |- | ||

| + | | 9 || U18 || U31 | ||

| + | |- | ||

| + | | 10 || U5 || U30 | ||

| + | |- | ||

| + | | 11 || U17 || U29 | ||

| + | |- | ||

| + | | 12 || U4 || U16 | ||

| + | |- | ||

| + | | 13 || U3 || U28 | ||

| + | |- | ||

| + | | 14 || U2 || U15 | ||

| + | |- | ||

| + | | 15 || U14 || U27 | ||

| + | |- | ||

| + | | P0 || U1 || U26 | ||

| + | |- | ||

| + | | P1 || U13 || U25 | ||

| + | |} | ||

| + | |||

| + | Facing the board, with the handles at the top, and the contacts at the bottom, the memory chips are numbered from U1 to U12, from left to right, in the top row; from U13 to U24 in the middle row; and from U25 to U36 in the bottom row. (See diagram in the previous section.) | ||

| + | |||

| + | ==See also== | ||

| + | |||

| + | * [[National Semiconductor NS23M QBUS memory]] | ||

| + | |||

| + | ==External links== | ||

| + | |||

| + | * [http://shop-pdp.net/~stuff/PDFs/National/National_NS23C.pdf Technical Manual NS23C 256KB/1MB Memory] (includes schematics) | ||

| + | |||

| + | [[Category: QBUS Memories]] | ||

Latest revision as of 12:12, 22 September 2022

The National Semiconductor NS23C is a QBUS main memory card in dual QBUS card-size format, with a maximum capacity of 256 Kbyte (using 64Kx1 DRAMs), or 1 Mbyte (un-documented, using 256Kx1 DRAMs). (The card may be configured to provide less memory than is physically present.)

It provides byte parity, and supports QBUS Block Mode. (Note that block mode must be disabled on older LSI-11 systems, including the LSI-11/2.) Internal or external memory refresh may be used

Contents

Identification

Unlike the NS23M, the NS23C printed circuit board does contain identification which indicates that it is an NS23C; in addition, the PCB says "PWB 551010105-002" on the solder side, and "PWA 980010105" on the component side.

256KB to 1M Upgrade

It is very easy to upgrade these cards from 256KB to 1MB, as it has all the necessary traces, jumpers, etc for this capability built into the card - even though the NS23C documentation says nothing about this capability!

Looking at the prints, the memory chips have all 9 address lines wired (unlike the very similar NS23M card), and there are several jumpers that adapt the card to 1MB operation. The chips are all in chip sockets, so pulling the 64Kx1's and replacing them with 256Kx1's is easy.

There are three 'jumpers' one has to remove/move; alas, they are traces in the PCB on the top surface, although there are jumper pins there - as built, there is a trace running between the two pins - so those traces have to be cut.

The first two 'jumpers' one has to remove are W23 and W24 (right next to the other memory size jumpers), which allow one to increase the maximum memory size to 1MB.

The other 'jumper' one has to do is to move the 'jumper' from W40 to W41; this moves the pickup point for the 'RS0' signal, which indicates which bank of chips (there are 2x18 banks, i.e. 16 data, and separate byte parity) to activate, from address line 17 to 19.

Control and Status Register

The NS23C has an optional Control and Status Register, which may be configured, and can be placed at one of eight locations. The layout is:

| Parity Error | Extended CSR Enable | Unused | A17-A15 | A21-A18 or A14-A11 |

Unused | Write Wrong Parity | Unused | Parity Error Enable | |||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

Configuration

Since the 1 Mbyte option is un-documented, here is updated information on how to configure the board.

Size

First, the low-order size bits, which are the same as the un-modified board:

| Size (Decimal) |

Size (Octal) |

Jumpers | |||

|---|---|---|---|---|---|

| W22 | W21 | W20 | W19 | ||

| 16KB | 000000 | I | I | I | I |

| 32KB | 010000 | I | I | I | R |

| 48KB | 020000 | I | I | R | I |

| 64KB | 030000 | I | I | R | R |

| 80KB | 040000 | I | R | I | I |

| 96KB | 050000 | I | R | I | R |

| 112KB | 060000 | I | R | R | I |

| 128KB | 400000 | I | R | R | R |

| 144KB | 440000 | R | I | I | I |

| 160KB | 500000 | R | I | I | R |

| 176KB | 540000 | R | I | R | I |

| 192KB | 600000 | R | I | R | R |

| 208KB | 640000 | R | R | I | I |

| 224KB | 700000 | R | R | I | R |

| 240KB | 740000 | R | R | R | I |

| 256KB | 1000000 | R | R | R | R |

and now the high-order size bits, which were not previously documented:

| Size (Decimal) |

Size (Octal) |

Jumpers | |

|---|---|---|---|

| W24 | W23 | ||

| 256KB | 1000000 | I | I |

| 512KB | 2000000 | I | R |

| 768KB | 3000000 | R | I |

| 1024KB | 4000000 | R | R |

Address

The starting address is also entirely the same as the un-modified board; first, the low-order starting address bits:

| Starting Address (Decimal) |

Starting Address (Octal) |

Jumpers | ||||

|---|---|---|---|---|---|---|

| W10 | W11 | W12 | W13 | W14 | ||

| 0KB | 000000 | R | R | R | R | R |

| 8KB | 020000 | I | R | R | R | R |

| 16KB | 040000 | R | I | R | R | R |

| 24KB | 060000 | I | I | R | R | R |

| 32KB | 100000 | R | R | I | R | R |

| 40KB | 120000 | I | R | I | R | R |

| 48KB | 1400000 | R | I | I | R | R |

| 56KB | 160000 | I | I | I | R | R |

| 64KB | 200000 | R | R | R | I | R |

| 72KB | 220000 | I | R | R | I | R |

| 80KB | 240000 | R | I | R | I | R |

| 88KB | 260000 | I | I | R | I | R |

| 96KB | 300000 | R | R | I | I | R |

| 104KB | 320000 | I | R | I | I | R |

| 112KB | 340000 | R | I | I | I | R |

| 120KB | 360000 | I | I | I | I | R |

| 128KB | 400000 | R | R | R | R | I |

| 136KB | 420000 | I | R | R | R | I |

| 144KB | 440000 | R | I | R | R | I |

| 152KB | 460000 | I | I | R | R | I |

| 160KB | 500000 | R | R | I | R | I |

| 168KB | 520000 | I | R | I | R | I |

| 176KB | 540000 | R | I | I | R | I |

| 184KB | 560000 | I | I | I | R | I |

| 192KB | 600000 | R | R | R | I | I |

| 200KB | 620000 | I | R | R | I | I |

| 208KB | 640000 | R | I | R | I | I |

| 216KB | 660000 | I | I | R | I | I |

| 224KB | 700000 | R | R | I | I | I |

| 232KB | 720000 | I | R | I | I | I |

| 240KB | 740000 | R | I | I | I | I |

| 248KB | 760000 | I | I | I | I | I |

and then the high-order starting address bits:

| Starting Address (Decimal) |

Starting Address (Octal) |

Jumpers | |||

|---|---|---|---|---|---|

| W15 | W16 | W17 | W18 | ||

| 0KB | 00000000 | R | R | R | R |

| 256KB | 01000000 | I | R | R | R |

| 512KB | 02000000 | R | I | R | R |

| 768KB | 03000000 | I | I | R | R |

| 1024KB | 04000000 | R | R | I | R |

| 1280KB | 05000000 | I | R | I | R |

| 1536KB | 06000000 | R | I | I | R |

| 1792KB | 07000000 | I | I | I | R |

| 2048KB | 10000000 | R | R | R | I |

| 2304KB | 11000000 | I | R | R | I |

| 2560KB | 12000000 | R | I | R | I |

| 2816KB | 13000000 | I | I | R | I |

| 3072KB | 14000000 | R | R | I | I |

| 3328KB | 15000000 | I | R | I | I |

| 3584KB | 16000000 | R | I | I | I |

| 3840KB | 17000000 | I | I | I | I |

Other

CSR Address:

| Address | Jumpers | ||

|---|---|---|---|

| W9 | W8 | W7 | |

| 772100 | I | I | I |

| 772102 | R | I | I |

| 772104 | I | R | I |

| 772106 | R | R | I |

| 772110 | I | I | R |

| 772112 | R | I | R |

| 772114 | I | R | R |

| 772116 | R | R | R |

Extended QBUS address type:

| Address Type | Jumpers | |||

|---|---|---|---|---|

| W47 | W48 | W49 | W50 | |

| 18-bit | R | R | R | R |

| 19-bit | I | R | R | R |

| 20-bit | I | I | R | R |

| 21-bit | I | I | R | I |

| 22-bit | I | I | I | I |

Other:

| Jumper | Function | Jumpers | |

|---|---|---|---|

| In | Out | ||

| W1 | Battery backup | None | Use |

| W2 | Use | None | |

| W3 | Refresh | Internal | External |

| W4 | External | Internal | |

| W5 | BREF Inhibit | Non-Inhibit | |

| W6 | Non-Inhibit | BREF Inhibit | |

| W27 | CSR | Enable | Disable |

| W28 | Disable | Enable | |

| W30 | Block Mode | Disable | Enable |

| W31 | Enable | Disable | |

| W35 | Parity Enable | Disabled | Enabled |

| W36 | I/O Page | 1 KW | 2/4 KW |

| W37 | 1/2 KW | 4 KW | |

All other jumpers are manufacturing-related; leave as they are.

Fault Isolation

The way the address logic works on the card is slightly odd; if the card is not on a 'natural' boundary [e.g. a 256KB boundary, if it's a 256KB card], the memory contents are scrambled; the low memory, in bus address terms, is at the top of the card, in chip terms, and the high memory, in bus terms, is at the bottom of the card.

They did it that way because that's the most economical way to do it in logic/traces, etc but it's something one would have to remember when looking for a bad memory chip, if the card is set to an address which is not a multiple of its size.

Chip Table

To aid fault isolation, here is a table which relates bit numbers in memory words to chip numbers:

| Bit | Low Bank | High Bank |

|---|---|---|

| 0 | U12 | U24 |

| 1 | U11 | U36 |

| 2 | U10 | U23 |

| 3 | U22 | U35 |

| 4 | U9 | U34 |

| 5 | U21 | U33 |

| 6 | U8 | U20 |

| 7 | U7 | U32 |

| 8 | U6 | U19 |

| 9 | U18 | U31 |

| 10 | U5 | U30 |

| 11 | U17 | U29 |

| 12 | U4 | U16 |

| 13 | U3 | U28 |

| 14 | U2 | U15 |

| 15 | U14 | U27 |

| P0 | U1 | U26 |

| P1 | U13 | U25 |

Facing the board, with the handles at the top, and the contacts at the bottom, the memory chips are numbered from U1 to U12, from left to right, in the top row; from U13 to U24 in the middle row; and from U25 to U36 in the bottom row. (See diagram in the previous section.)

See also

External links

- Technical Manual NS23C 256KB/1MB Memory (includes schematics)