Difference between revisions of "National Semiconductor NS23M QBUS memory"

(Add chip table) |

m (+links) |

||

| (6 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

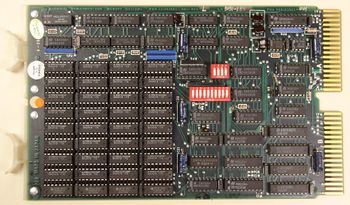

| − | The '''National Semiconductor NS23M''' is a [[QBUS]] memory card in [[DEC card form factor|dual]] QBUS card-size format. It can be configured to use either 16Kx1, 32Kx1 or 64Kx1 [[ | + | [[Image:NS23M.jpg|350px|right|thumb|NS23M card]] |

| + | |||

| + | The '''National Semiconductor NS23M''' is a [[QBUS]] [[main memory]] card in [[DEC card form factor|dual]] QBUS card-size format. It can be configured to use either 16Kx1, 32Kx1 or 64Kx1 [[Dynamic RAM|DRAMs]], operating at 150nsec or 200nsec; it has a maximum capacity of 256 Kbyte (using 64Kx1 DRAMs). It provides byte [[parity]]. | ||

==Identification== | ==Identification== | ||

| − | Unlike the [[National Semiconductor NS23C QBUS memory|NS23C]], the NS23M [[printed circuit board]] does not contain any identification which indicates directly that it is an NS23M. The PCB only says "PWB 551103882-003" and "PWA 980103882", both on the component side; one often sees these boards listed on auction sites under these ids. | + | Unlike the [[National Semiconductor NS23C QBUS memory|NS23C]], the NS23M [[printed circuit board]] '''does not''' contain any identification which indicates directly that it is an NS23M. The PCB only says "PWB 551103882-003" and "PWA 980103882", both on the component side; one often sees these boards listed on auction sites under these ids. |

== Configuration== | == Configuration== | ||

| − | The board is configured with a combination of | + | The board is configured with a combination of [[jumper]]s and [[Dual Inline Package|DIP]] switches. |

{| class="wikitable" | {| class="wikitable" | ||

| Line 20: | Line 22: | ||

| W8-W9 || Test | | W8-W9 || Test | ||

|- | |- | ||

| − | | W10-W11 || Internal/External | + | | W10-W11 || Internal/External [[memory refresh]] |

|- | |- | ||

| W13-W14 || 32K DRAM Upper/Lower | | W13-W14 || 32K DRAM Upper/Lower | ||

| Line 34: | Line 36: | ||

{| class="wikitable" | {| class="wikitable" | ||

| − | ! Switch !! Address bit | + | ! Switch !! Address bit !! Location |

|- | |- | ||

| − | | S1-1 || | + | | S1-1 || 020000 || 8KB |

|- | |- | ||

| − | | S1-2 || | + | | S1-2 || 040000 || 16KB |

|- | |- | ||

| − | | S1-3 || | + | | S1-3 || 0100000 || 32KB |

|- | |- | ||

| − | | S1-4 || | + | | S1-4 || 0200000 || 64KB |

|- | |- | ||

| − | | S1-5 || | + | | S1-5 || 0400000 || 128KB |

|- | |- | ||

| − | | S1-6 || | + | | S1-6 || 01000000 || 256KB |

|- | |- | ||

| − | | S1-7 || | + | | S1-7 || 02000000 || 512KB |

|- | |- | ||

| − | | S1-8 || | + | | S1-8 || 04000000 || 1024KB |

|- | |- | ||

| − | | S1-9 || | + | | S1-9 || 010000000 || 2048KB |

|} | |} | ||

| Line 75: | Line 77: | ||

==Fault Isolation== | ==Fault Isolation== | ||

| − | To aid fault isolation, here is a table which relates bit numbers in memory words to chip | + | To aid [[QBUS memories#Diagnosing DRAM memory failures|fault isolation]], here is a table which relates bit numbers in memory words to chip numbers: |

{| class="wikitable" | {| class="wikitable" | ||

| Line 118: | Line 120: | ||

Facing the board, with the handles at the top, and the contacts at the bottom, the memory chips are numbered from U1 to U9, from left to right, in the top row; from U10 to U18 in the upper middle row; from U19 to U27 in the lower middle row; and from U28 to U36 in the bottom row. | Facing the board, with the handles at the top, and the contacts at the bottom, the memory chips are numbered from U1 to U9, from left to right, in the top row; from U10 to U18 in the upper middle row; from U19 to U27 in the lower middle row; and from U28 to U36 in the bottom row. | ||

| + | |||

| + | ==See also== | ||

| + | |||

| + | * [[National Semiconductor NS23C QBUS memory]] | ||

| + | |||

| + | ==External links== | ||

| + | |||

| + | * [http://ana-3.lcs.mit.edu/~jnc/tech/pdp11/NS23/NS23M.pdf NS23M Installation Guide] (includes schematics) | ||

| + | |||

| + | [[Category: QBUS Memories]] | ||

Latest revision as of 12:18, 22 September 2022

The National Semiconductor NS23M is a QBUS main memory card in dual QBUS card-size format. It can be configured to use either 16Kx1, 32Kx1 or 64Kx1 DRAMs, operating at 150nsec or 200nsec; it has a maximum capacity of 256 Kbyte (using 64Kx1 DRAMs). It provides byte parity.

Contents

Identification

Unlike the NS23C, the NS23M printed circuit board does not contain any identification which indicates directly that it is an NS23M. The PCB only says "PWB 551103882-003" and "PWA 980103882", both on the component side; one often sees these boards listed on auction sites under these ids.

Configuration

The board is configured with a combination of jumpers and DIP switches.

| Jumper(s) | Function |

|---|---|

| W1-W2, W17-W18 | 200ns/150ns DRAM |

| W3-W4 | Test |

| W5-W7, W12 | 16K/32K/64K DRAM |

| W8-W9 | Test |

| W10-W11 | Internal/External memory refresh |

| W13-W14 | 32K DRAM Upper/Lower |

| W15 | 18-/22-bit QBUS (in/out) |

| W16 | External Refresh / MEMSEL |

| W19-W20 | Battery Backup |

Starting Address

| Switch | Address bit | Location |

|---|---|---|

| S1-1 | 020000 | 8KB |

| S1-2 | 040000 | 16KB |

| S1-3 | 0100000 | 32KB |

| S1-4 | 0200000 | 64KB |

| S1-5 | 0400000 | 128KB |

| S1-6 | 01000000 | 256KB |

| S1-7 | 02000000 | 512KB |

| S1-8 | 04000000 | 1024KB |

| S1-9 | 010000000 | 2048KB |

Size

| Jumper(s) | Function |

|---|---|

| S2-1 | 16KB |

| S2-2 | 32KB |

| S2-3 | 64KB |

| S2-4 | 128KB |

| S1-10 | 2K/4K I/O Address Space (closed/open) |

Note that the size is the value indicated, plus 16KB (the minimum); i.e. 0000 = 16KB, 1111 = 256KB.

Fault Isolation

To aid fault isolation, here is a table which relates bit numbers in memory words to chip numbers:

| Bit | Low Bank | High Bank |

|---|---|---|

| 0 | U12 | U24 |

| 1 | U11 | U36 |

| 2 | U10 | U23 |

| 3 | U22 | U35 |

| 4 | U9 | U34 |

| 5 | U21 | U33 |

| 6 | U8 | U20 |

| 7 | U7 | U32 |

| 8 | U6 | U19 |

| 9 | U18 | U31 |

| 10 | U5 | U30 |

| 11 | U17 | U29 |

| 12 | U4 | U16 |

| 13 | U3 | U28 |

| 14 | U2 | U15 |

| 15 | U14 | U27 |

| P0 | U1 | U26 |

| P1 | U13 | U25 |

Facing the board, with the handles at the top, and the contacts at the bottom, the memory chips are numbered from U1 to U9, from left to right, in the top row; from U10 to U18 in the upper middle row; from U19 to U27 in the lower middle row; and from U28 to U36 in the bottom row.

See also

External links

- NS23M Installation Guide (includes schematics)