Difference between revisions of "DLV11-F asynchronous serial line interface"

(Fairly complete) |

(+img) |

||

| Line 1: | Line 1: | ||

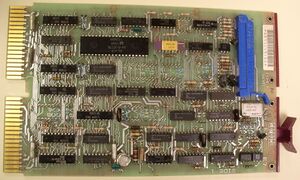

| + | [[Image:DLV11-F RevD.jpg|thumb|right|300px|DLV11-F M8028 board etch revision D]] | ||

| + | |||

The '''DLV11-F asynchronous serial line interface''' card (M8028) was a [[QBUS]] [[peripheral]] for the [[PDP-11]] series of computers which provided an [[asynchronous serial line]] on a single [[DEC card form factor|dual-width]] card. | The '''DLV11-F asynchronous serial line interface''' card (M8028) was a [[QBUS]] [[peripheral]] for the [[PDP-11]] series of computers which provided an [[asynchronous serial line]] on a single [[DEC card form factor|dual-width]] card. | ||

| Line 15: | Line 17: | ||

==Layout== | ==Layout== | ||

| − | The 'Revison C' [[printed circuit board|PCB]] | + | The 'Revison C' and later [[printed circuit board|PCB]] layouts are significantly different from the earlier ones; it is easy to recognize these versions visually, as the large [[asynchronous serial line#UART|UART]] chip is parallel to the long axis of the card. These versions are not covered in most DLV11-F documentation; they can be found in the ''"Microcomputer Interfaces Handbook"'' (1983-84), on pg. 244. |

==See also== | ==See also== | ||

Revision as of 22:25, 16 October 2020

The DLV11-F asynchronous serial line interface card (M8028) was a QBUS peripheral for the PDP-11 series of computers which provided an asynchronous serial line on a single dual-width card.

It provided both EIA RS-232 (with vestigial modem control), and active or passive 20 mA connectivity. Baud rates from 50 to 19,200 were available; receive and transmit can be set independently via configuration jumpers, or can be set via the registers, if desired (although not independently; either transmit only, or both).

Line connection was via 40-pin Berg connector headers on the top edge of the card, using the standard DEC asynchronous serial line pinout.

Programing interface

Like the ancestral KL11, the DLV11 has 2 device registers for the receive side (one Control and Status Register - CSR - and one data buffer register), and similarly, two for the transmit side. Each line has two interrupt vectors - again, one receive, and one transmit.

For the PDP-11 main console (which is always a KL11/DL11 compatible device), the standard is that 0777560 is the base address (so the receiver registers are 0777560-2, and the transmitter are 0777564-6), and 060 is the base vector. It can be set to halt the CPU when a 'break' is seen; it can also send a 'break'.

The first line after the console is always assigned the address 0776500, and vector 0300. Additional lines are assigned addresses and vectors immediately following, for DL11's #1-#16 (i.e. 0776500-676 and 0300-0476).

Layout

The 'Revison C' and later PCB layouts are significantly different from the earlier ones; it is easy to recognize these versions visually, as the large UART chip is parallel to the long axis of the card. These versions are not covered in most DLV11-F documentation; they can be found in the "Microcomputer Interfaces Handbook" (1983-84), on pg. 244.