PDP-8/E

From Computer History Wiki

| PDP-8/E | |

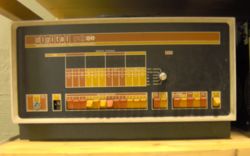

PDP-8/E front panel | |

| Year Introduced: | 1970 |

|---|---|

| Form Factor: | minicomputer |

| Word Size: | 12 |

| Logic Type: | TTL |

| Design Type: | clocked random logic |

| Clock Speed: | 385KHz |

| Memory Speed: | 1.2 μseconds |

| Physical Address Size: | 32KW (requires optional KM8-E) |

| Virtual Address Size: | 4KW |

| Memory Management: | bank selection, CPU mode |

| Bus Architecture: | OMNIBUS |

| Operating System: | OS/8, TSS/8 |

| Predecessor(s): | PDP-8/I |

| Successor(s): | PDP-8/A |

The PDP-8/E was an improved model in the PDP-8 line, and introduced the OMNIBUS for interfacing to device controllers.

The PDP-8/F was a cost-reduced version of the -8/E with the same CPU and main memory, but only a single OMNIBUS backplane. The PDP-8/M is the OEM version of the PDP-8/F.

It could perform an addition to the accumulator in 2.6 microseconds, and a 12 by 12 bit multiplication with 24 bit result in 40 microseconds with the math extension hardware.

| v • d • e PDP-8 Computers, Software and Peripherals |

|---|

| PDP-8s: PDP-5 • PDP-8 • LINC-8 • PDP-8/S • PDP-8/I • PDP-8/L • PDP-12 • PDP-8/E • PDP-8/F • PDP-8/M • PDP-8/A

Workstations: VT78 Also: PDP-8 family • PDP-8 architecture • PDP-8 Memory Extension units |