Interlan NI1010A/NI2010A Ethernet Communications Controller

The Interlan NI1010A and NI2010A are Ethernet network interfaces for the UNIBUS and QBUS respectively. (The two device controllers are very similar in programming terms, in part because they use the same daughter-board to implement all the networking functionality, so they are both covered in this single article.)

They use DMA to transfer data to and from buffers in main memory. They have an on-board FIFO buffer which can hold up to 13.5K bytes of inbound data; the host can pre-queue up to 16 input buffer DMA requests.

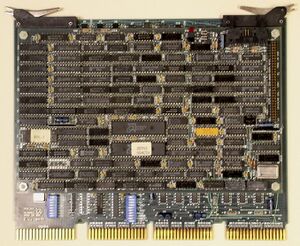

The NI1010A is a single hex board, including a large daughter-board laid flush on the main PCB. The NI2010A is a quad board, with the daughter-board stacked above the main PDB, which is filled with ICs. It therefore takes up two slots, but only the mother card has edge fingers to plug in; a grant continuity card is supplied, to plug into the second slot, to carry the QBUS' bus grant lines through the second slot.

Their bus address and interrupt vectors can be set via DIP switches on the mother-board; to 7mnnp0 for the address (where m can be 6 or 7, and p 0,2,4 or 6), and 0xx0 for the vector. Their defaults are 0764000 and 0340.

There are two interrupt vectors; 0xx0 for 'Receive DMA done' and 0xx4 for 'Command done'.

Contents

Device registers

The NI1010A controller includes 3 registers, and the NI2010A 4 (the optional extra register is needed because of the larger address space on the QBUS):

| Register | Abbreviation | Address |

|---|---|---|

| Control Status Register | CSR | 764000 |

| Bus Address Register | BAR | 764002 |

| Byte Count Register | BCR | 764004 |

| Bus Address Extension Register NI2010A only |

BER | 17764006 |

The Bus Address Extension Register was enabled by a switch; i.e. the NI2010A could be set to be identical, programmatically, to the NI1010A, at the cost of not being able to use more than 256KB of main memory.

In the register contents (below), bits which are read/write or unused are shown in normal font, those which are read-only are in italics, and those which are write-only are shown in bold.

764000: Control Status Register (CSR)

| XM | FUNC | CDN | CIE | RDN | RIE | STAT | |||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

Bits are:

| Bits | Use |

|---|---|

| XM | Extended address bits A17 and A16 |

| FUNC | Command Function Code |

| CDN | Command Done |

| CIE | Command Done Interrupt Enable |

| RDN | Receive DMA Done |

| RIE | Receive DMA Done Interrupt Enable |

| STAT | Command Status Code |

Reading the CSR clears the two 'done' bits. The extended address bits are disabled on the NI2010A when the BER is enabled.

Command function codes are:

| Code | Command |

|---|---|

| 01 | Set loopback |

| 02 | Set internal loopback |

| 03 | Clear loopback |

| 04 | Set promiscuous receive |

| 05 | Clear promiscuous receive |

| 06 | Set receive-on-error |

| 07 | Clear receive-on-error |

| 10 | Go offline |

| 11 | Go online |

| 12 | Run diagnostic |

| 15 | Set insert source address |

| 16 | Clear insert source address |

| 17 | Set network address to default |

| 20 | Set receive all multicast |

| 21 | Clear receive all multicast |

| 22 | Perform loopback test |

| 23 | Perform collision detection test |

| 30 | Report and clear stats |

| 31 | Report collision delay times |

| 40 | Supply receive buffer |

| 50 | Load transmit data |

| 51 | Load transmit data and send |

| 52 | Load group address(es) |

| 53 | Delete group address(es) |

| 54 | Load physical network address |

| 60 | Flush input buffer queue |

| 77 | Reset |

Command status codes are:

| Code | Status |

|---|---|

| 00 | Success |

| 01 | Success with retries |

| 02 | Illegal command |

| 03 | Inappropriate command |

| 04 | Failure |

| 05 | Buffer size exceeded |

| 06 | Frame too small |

| 10 | Excessive collisions |

| 12 | Buffer alignment error |

| 13 | No heartbeat detected |

| 14 | No CRC error occurred |

| 15 | Inappropriate CRC error |

| 16 | Last data byte not received |

| 17 | Non-existent memory |

764002: Bus Address Register (BAR)

| BA15 <---> BA00 | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

Write-only register.

764004: Byte Count Register (BCR)

| BC15 <---> BC0 | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

Write-only register.

17764006: Bus Address Extension Register (BER)

| Unused | BA21 <---> BA16 | ||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

Write-only register.

Note: This register is optionally present in the NI2010A only.

External links

- NI1010A Unibus Ethernet Communications Controller - detailed sales brochure

- NI2010A Qbus Ethernet Communications Controller - sales brochure

- NI1010A UNIBUS Ethernet Communications Controller User's Manual