Difference between revisions of "KDF11-B CPU"

m (+links, refactor a bit) |

m (+KDF11-B CPU System Maintenance) |

||

| (3 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

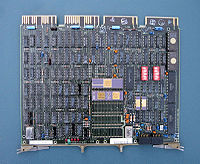

| − | [[Image:M8189.jpg|200px|thumb|right|M8189]] | + | [[Image:M8189.jpg|200px|thumb|right|KDF11-BA M8189 card, with KTF11-A MMU chip]] |

The '''KDF11-B''' [[PDP-11 architecture|PDP-11]] [[Central Processing Unit|CPU]] for the [[PDP-11/23_PLUS|PDP-11/23+]] was implemented as a single [[DEC card form factor|quad]] card, the KDF11-BA M8189, using the same 'Fonz' [[F-11 chip set]] as the other [[KDF11 CPUs]]. | The '''KDF11-B''' [[PDP-11 architecture|PDP-11]] [[Central Processing Unit|CPU]] for the [[PDP-11/23_PLUS|PDP-11/23+]] was implemented as a single [[DEC card form factor|quad]] card, the KDF11-BA M8189, using the same 'Fonz' [[F-11 chip set]] as the other [[KDF11 CPUs]]. | ||

| Line 5: | Line 5: | ||

In addition to the basic CPU functionality, it included [[chip socket]]s for adding the [[KTF11-A memory management chip|KTF11-A]] ([[PDP-11 Memory Management|memory management]]) and the [[KEF11-A floating point chip|KEF11-A]] ([[FP11 floating point]]). The sockets can also hold the [[KEF11-B CIS chip|KEF11-B]] 6-chip carrier implementing the [[PDP-11 Commercial Instruction Set]]. | In addition to the basic CPU functionality, it included [[chip socket]]s for adding the [[KTF11-A memory management chip|KTF11-A]] ([[PDP-11 Memory Management|memory management]]) and the [[KEF11-A floating point chip|KEF11-A]] ([[FP11 floating point]]). The sockets can also hold the [[KEF11-B CIS chip|KEF11-B]] 6-chip carrier implementing the [[PDP-11 Commercial Instruction Set]]. | ||

| − | The board also contains sockets for [[PROM]]s (for [[bootstrap|booting]] and [[diagnostic]]s) | + | The board also contains sockets for [[PROM]]s (for [[bootstrap|booting]] and [[diagnostic]]s); [[KW11-L Line Time Clock|KW11-L]] [[line time clock]] functionality; and two [[asynchronous serial line]]s. |

| − | + | Line connection was via two separate 10-pin [[Berg connector]] headers on the top edge of the card, using the standard 10-[[pin]] [[DEC asynchronous serial line pinout]]. They both provided [[EIA RS-232 serial line interface|EIA RS-232]] connectivity, at speeds of 50 to 19.2K [[baud rate|baud]] (when using the on-board clock); on both lines, receive and transmit speeds are the same, but the speed of each line could be set independently. | |

| − | [[ | + | ==Cabling== |

| − | [[Category: QBUS Processors]] | + | |

| + | There are several options for cabling to the serial line ports on the KDF11-B. One is to run individual cables, such as the BC20N-xx (Berg 10-pin connector, to a [[EIA RS-232 serial line interface#Connectors|female DB-25S connector]] wired as a DCE - i.e. including a [[EIA RS-232 serial line interface|null modem]]) to each line's Berg connector. | ||

| + | |||

| + | The alternative approach is that DEC produced a number of distribution panels which can be used with the KDF11-B; all have a [[flat cable]] which splits into two sub-cables, each with a Berg 10-pin connector which plugs into one of the Berg headers. One is the D315; in the variant applicable to the KDF11-B, it has two male DB-25P connectors (the [[printed circuit board|PCB]] has locations for four, but only two are used), wired as a DTEs. | ||

| + | |||

| + | A more flexible choice is the [[PDP-11/23 PLUS]] [[cabinet kit]] (also called a 'Patch and Filter Panel' in some DEC documentation), [[DEC part number]] 54-15422-01; it consists of a flat cable (split as above) with a Berg connector, plugged into a [[distribution panel]] which contains two male DB-25P connectors, and two rotary selectors which select a baud rate. Note: use of this requires [[jumper]]s on the CPU card to select the use of an external baud rate clock signal. | ||

| + | |||

| + | ==External links== | ||

| + | |||

| + | * [http://www.bitsavers.org/pdf/dec/pdp11/1123/EK-KDF11-UG-PR2_Mar79.pdf KDF11-BA CPU Module User's Guide] (EK-KDFEB-UG-001) | ||

| + | * [http://www.bitsavers.org/scandocs.trailing-edge.com/micropdp11-volume1_system_cpus-EK-245AA-MG-001.pdf KDF11-B CPU System Maintenance] (EK-245AA-MG-001) | ||

| + | * [http://www.bitsavers.org/pdf/dec/pdp11/1123/MP01236_KDF11-B_schem.pdf KDF11-B Field Maintenance Print Set] (MP01236) | ||

| + | |||

| + | [[Category: PDP-11 QBUS Processors]] | ||

Latest revision as of 08:58, 29 March 2022

The KDF11-B PDP-11 CPU for the PDP-11/23+ was implemented as a single quad card, the KDF11-BA M8189, using the same 'Fonz' F-11 chip set as the other KDF11 CPUs.

In addition to the basic CPU functionality, it included chip sockets for adding the KTF11-A (memory management) and the KEF11-A (FP11 floating point). The sockets can also hold the KEF11-B 6-chip carrier implementing the PDP-11 Commercial Instruction Set.

The board also contains sockets for PROMs (for booting and diagnostics); KW11-L line time clock functionality; and two asynchronous serial lines.

Line connection was via two separate 10-pin Berg connector headers on the top edge of the card, using the standard 10-pin DEC asynchronous serial line pinout. They both provided EIA RS-232 connectivity, at speeds of 50 to 19.2K baud (when using the on-board clock); on both lines, receive and transmit speeds are the same, but the speed of each line could be set independently.

Cabling

There are several options for cabling to the serial line ports on the KDF11-B. One is to run individual cables, such as the BC20N-xx (Berg 10-pin connector, to a female DB-25S connector wired as a DCE - i.e. including a null modem) to each line's Berg connector.

The alternative approach is that DEC produced a number of distribution panels which can be used with the KDF11-B; all have a flat cable which splits into two sub-cables, each with a Berg 10-pin connector which plugs into one of the Berg headers. One is the D315; in the variant applicable to the KDF11-B, it has two male DB-25P connectors (the PCB has locations for four, but only two are used), wired as a DTEs.

A more flexible choice is the PDP-11/23 PLUS cabinet kit (also called a 'Patch and Filter Panel' in some DEC documentation), DEC part number 54-15422-01; it consists of a flat cable (split as above) with a Berg connector, plugged into a distribution panel which contains two male DB-25P connectors, and two rotary selectors which select a baud rate. Note: use of this requires jumpers on the CPU card to select the use of an external baud rate clock signal.

External links

- KDF11-BA CPU Module User's Guide (EK-KDFEB-UG-001)

- KDF11-B CPU System Maintenance (EK-245AA-MG-001)

- KDF11-B Field Maintenance Print Set (MP01236)