Difference between revisions of "PDP-8/E"

m (→External links: +Good collector site) |

(12-bit cat.) |

||

| Line 67: | Line 67: | ||

[[Category: PDP-8s]] | [[Category: PDP-8s]] | ||

| + | [[Category: 12-bit Computers]] | ||

Revision as of 11:45, 11 July 2023

| PDP-8/E | |

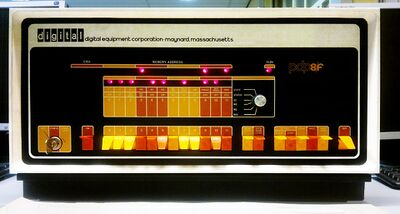

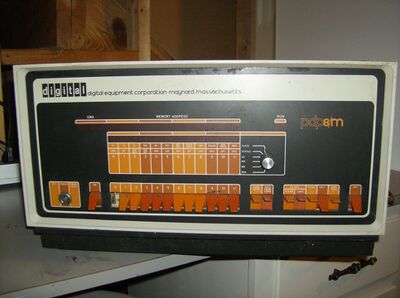

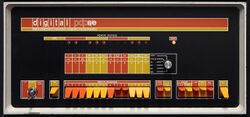

PDP-8/E front panel | |

| Manufacturer: | DEC |

|---|---|

| Architecture: | PDP-8 |

| Year Introduced: | 1970 |

| Form Factor: | minicomputer |

| Word Size: | 12 |

| Logic Type: | TTL |

| Design Type: | clocked random logic |

| Clock Speed: | 385KHz |

| Memory Speed: | 1.2 μseconds |

| Physical Address Size: | 32KW (requires optional KM8-E) |

| Virtual Address Size: | 4KW |

| Memory Management: | bank selection, CPU mode |

| Bus Architecture: | OMNIBUS |

| Operating System: | OS/8, TSS/8 |

| Predecessor(s): | PDP-8/I |

| Successor(s): | PDP-8/A |

| Price: | US$5K (CPU and 4KW memory) |

The PDP-8/E was an improved model in the PDP-8 line from DEC, and introduced the OMNIBUS for interfacing to device controllers.

The PDP-8/F was a cost-reduced version of the -8/E with the same CPU, but only a single OMNIBUS backplane. The PDP-8/M is the OEM version of the PDP-8/F. Both the /E and /M used the H9191-9216 20-slot quad-width OMNIBUS backplane.

The -8/E-F-M's KK8-E CPU consists of five quad boards (M8300 Major Registers, M8310 Register Control, M8320 Bus Loads, M8330 Timing Generator, M8560 Teletype Control); its standard main memory was the MM8-E Memory System core memory, which initially came in 4K word blocks.

Options included:

- KA8-E Positive I/O Bus Interface, to allow use of older PDP-8 devices

- KM8-E Memory Extension and Time-Share Option, which provided the bank switching needed to support more than 4KW of memory, and allowed the computer to operate in either Executive Mode or User Mode (some sources refer to this as the 'MC8/E' - probably by analogy with earlier PDP-8 Memory Extension units such as the MC8/I and MC8/L - but no DEC documentation refers to that name)

- MP8-E Memory Parity

- KD8-E Data Break Interface

- KE8-E Extended Arithmetic Element (two quad boards), which supported hardware integer multiplication and division, one-bit double-word shifts, and normalization

- FPP12-P and FPP12-AP Floating Point Processor (24+12 bits)

- FPP12-AE Double Precision option (FPP12-AP only, 60+12 bits)

It could perform an addition to the accumulator in 2.6 μseconds, and a 12 by 12 bit multiplication with 24 bit result in 40 μseconds, using the math extension hardware.

The -8/M could be supplied with either a KC8-M Operator's Console, or a KC8-ML Programmer's Console, the latter being basically identical to the KC8-EA Programmer's Console of the basic -8/E.

Images

External links

- PDP-8/E documents

- PDP-8/E Illustrated Parts Breakdown

- PDP-8/E, PDP-8/F & PDP-8/M Maintenance Manual Volume 1 (DEC-8E-HMM1A-D-D) - also covers the MM8-E and Teletype Control

- First-Hand:PDP-8/E OMNIBUS Ride - PDP-8/E Design Story

- Digital PDP-8F

- A PDP-8/E Emulator in Java - lots of other PDP-8 content, too

- Manuals - mostly software, but some hardware

- PDP-8/M Restoration Project

| v • d • e PDP-8 Computers, Software and Peripherals |

|---|

| PDP-8s: PDP-5 • PDP-8 • LINC-8 • PDP-8/S • PDP-8/I • PDP-8/L • PDP-12 • PDP-8/E • PDP-8/F • PDP-8/M • PDP-8/A

Workstations: VT78 Also: PDP-8 family • PDP-8 architecture • PDP-8 Memory Extension units |