Difference between revisions of "KD11-A CPU"

(→Implementation: Add image of uword card) |

m (→Implementation: rm dup text) |

||

| (8 intermediate revisions by the same user not shown) | |||

| Line 3: | Line 3: | ||

Support for the [[PDP-11 Extended Instruction Set|EIS]] was optional, with the [[KE11-E Extended Instruction Set]], a hex card. There was also optional [[floating point]] hardware, the [[KE11-F Floating Instruction Set]], a quad card; it was not the full [[FP11 Floating Point]], but the minimal [[FIS floating point]]. | Support for the [[PDP-11 Extended Instruction Set|EIS]] was optional, with the [[KE11-E Extended Instruction Set]], a hex card. There was also optional [[floating point]] hardware, the [[KE11-F Floating Instruction Set]], a quad card; it was not the full [[FP11 Floating Point]], but the minimal [[FIS floating point]]. | ||

| − | [[Memory management]] support was also optional, with the [[KT11-D Memory Management]], another hex card; it too was not the full [[PDP-11 Memory Management]], but the simplified subset. | + | [[Memory management]] support was also optional, with the [[KT11-D Memory Management]], another hex card; it too was not the full [[PDP-11 Memory Management]], but the simplified subset. Other CPU options included the [[KJ11-A Stack Limit Register]], and the [[KW11-L Line Time Clock]] (the latter being a standard option across a number of PDP-11 CPUs). |

| − | + | It used the [[KY11-D Programmer's Console|KY11-D]] [[front panel]]. Provision was also made for two optional [[KM11-A Maintenance Set]]s, one for the KD11-A itself, and one for the other parts of the CPU (KE11-E, etc). | |

==Implementation== | ==Implementation== | ||

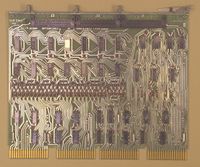

| − | [[Image:KD11A-M7232.jpg|thumb|right|200px|M7232 card from KD11-A | + | [[Image:KD11A-M7232.jpg|thumb|right|200px|M7232 card from KD11-A]] |

The basic KD11-A was contained on four [[DEC card form factor|hex]] cards: | The basic KD11-A was contained on four [[DEC card form factor|hex]] cards: | ||

| Line 22: | Line 22: | ||

* M7232 - μword | * M7232 - μword | ||

| − | The [[Berg connector]]s on the M7232 carry the microcode bus to the KE11-E EIS card; note also the metal handle on this card, even though it is only a quad card; the only non-[[QBUS]] quad | + | The [[Berg connector]]s on the M7232 carry the microcode bus to the optional KE11-E EIS card; note also the metal edge handle on this card, even though it is only a quad card; it and the KE11-F FIS card are the only non-[[QBUS]] quad cards known to have such a handle. |

| − | All of them plugged into a [[wire-wrap]]ped custom [[backplane]] dual [[system unit]]. The KE11-E Extended Instruction Set, KE11-F Floating Instruction Set, and KT11-D Memory Management option cards all plugged into pre-wired slots in this backplane, as did the KJ11-A Stack Limit Register and the KW11-L Line Time Clock. | + | All of them plugged into a [[wire-wrap]]ped custom 9-slot [[backplane]] dual [[system unit]]. The optional KE11-E Extended Instruction Set, KE11-F Floating Instruction Set, and KT11-D Memory Management option cards all plugged into pre-wired slots in this backplane, as did the KJ11-A Stack Limit Register and the KW11-L Line Time Clock. This left one unused slot, which was wired as a UNIBUS [[Small Peripheral Controller|SPC]] slot; that slot also contained the 'UNIBUS out'. |

| − | [[ | + | Board locations are: |

| − | [[Category:UNIBUS Processors]] | + | <!-- (as seen from the board insertion side of the backplane, not the wire-wrap pin side, as is common in [[Digital Equipment Corporation|DEC]] documentation) --> |

| + | |||

| + | {| class="wikitable" | ||

| + | ! !! colspan="6" | Connector | ||

| + | |- | ||

| + | ! Slot !! A !! B !! C !! D !! E !! F | ||

| + | |- | ||

| + | | 1 || colspan="4" style="text-align:center;" | M7239 FIS || style="text-align:center;" | KM11-A (KT, KE) || style="text-align:center;" | KM11-A (KD) | ||

| + | |- | ||

| + | | 2 || colspan="6" style="text-align:center;" | M7238 EIS | ||

| + | |- | ||

| + | | 3 || colspan="4" style="text-align:center;" | M7232 u Word || style="text-align:center;" | KJ11-A || style="text-align:center;" | KW11-L | ||

| + | |- | ||

| + | | 4 || colspan="6" style="text-align:center;" | M7231 Data Path | ||

| + | |- | ||

| + | | 5 || colspan="6" style="text-align:center;" | M7233 IR Decode | ||

| + | |- | ||

| + | | 6 || colspan="6" style="text-align:center;" | M7235 Status | ||

| + | |- | ||

| + | | 7 || colspan="6" style="text-align:center;" | M7234 Timing | ||

| + | |- | ||

| + | | 8 || colspan="6" style="text-align:center;" | M7236 KT11-D | ||

| + | |- | ||

| + | | 9 || colspan="2" style="text-align:center;" | UNIBUS Out || colspan="4" style="text-align:center;" | SPC | ||

| + | |} | ||

| + | |||

| + | <!-- ==Further reading== | ||

| + | --> | ||

| + | |||

| + | ==External links== | ||

| + | |||

| + | * [http://www.bitsavers.org/pdf/dec/pdp11/1140/DEC-11-HKDAA-A-D_KD11-A_Processor_Manual.pdf KD11-A processor manual] (DEC-11-HKDAA-A-D) | ||

| + | * [http://www.bitsavers.org/www.computer.museum.uq.edu.au/pdf/EK-KD11A-MM-001%20KD11-A%20Processor%20Maintenance%20Manual.pdf KD11-A processor maintenance manual] (EK-KD11A-MM-001) | ||

| + | * [http://www.bitsavers.org/pdf/dec/pdp11/1140/PDP-1140_System_Engr_Drawings_Rev_P_Jun74.pdf PDP-11/40 system engineering drawings] (pp. 9-108 of the PDF) | ||

| + | * [https://loomcom.com/blog/0044_what_makes_a_pdp_11_35_tick.html What Makes A PDP-11/35 Tick?] - List of chips in the KD11-A | ||

| + | |||

| + | [[Category: PDP-11 UNIBUS Processors]] | ||

Latest revision as of 03:52, 8 April 2024

The KD11-A PDP-11 CPU for the PDP-11/35 and PDP-11/40 was a multi-board micro-programmed processor.

Support for the EIS was optional, with the KE11-E Extended Instruction Set, a hex card. There was also optional floating point hardware, the KE11-F Floating Instruction Set, a quad card; it was not the full FP11 Floating Point, but the minimal FIS floating point.

Memory management support was also optional, with the KT11-D Memory Management, another hex card; it too was not the full PDP-11 Memory Management, but the simplified subset. Other CPU options included the KJ11-A Stack Limit Register, and the KW11-L Line Time Clock (the latter being a standard option across a number of PDP-11 CPUs).

It used the KY11-D front panel. Provision was also made for two optional KM11-A Maintenance Sets, one for the KD11-A itself, and one for the other parts of the CPU (KE11-E, etc).

Implementation

The basic KD11-A was contained on four hex cards:

- M7231 - Data Paths

- M7233 - IR Decode

- M7234 - Timing

- M7235 - Status

and one quad card:

- M7232 - μword

The Berg connectors on the M7232 carry the microcode bus to the optional KE11-E EIS card; note also the metal edge handle on this card, even though it is only a quad card; it and the KE11-F FIS card are the only non-QBUS quad cards known to have such a handle.

All of them plugged into a wire-wrapped custom 9-slot backplane dual system unit. The optional KE11-E Extended Instruction Set, KE11-F Floating Instruction Set, and KT11-D Memory Management option cards all plugged into pre-wired slots in this backplane, as did the KJ11-A Stack Limit Register and the KW11-L Line Time Clock. This left one unused slot, which was wired as a UNIBUS SPC slot; that slot also contained the 'UNIBUS out'.

Board locations are:

| Connector | ||||||

|---|---|---|---|---|---|---|

| Slot | A | B | C | D | E | F |

| 1 | M7239 FIS | KM11-A (KT, KE) | KM11-A (KD) | |||

| 2 | M7238 EIS | |||||

| 3 | M7232 u Word | KJ11-A | KW11-L | |||

| 4 | M7231 Data Path | |||||

| 5 | M7233 IR Decode | |||||

| 6 | M7235 Status | |||||

| 7 | M7234 Timing | |||||

| 8 | M7236 KT11-D | |||||

| 9 | UNIBUS Out | SPC | ||||

External links

- KD11-A processor manual (DEC-11-HKDAA-A-D)

- KD11-A processor maintenance manual (EK-KD11A-MM-001)

- PDP-11/40 system engineering drawings (pp. 9-108 of the PDF)

- What Makes A PDP-11/35 Tick? - List of chips in the KD11-A