Difference between revisions of "PDP-10 I/O Bus"

(Redirect for now, pending close of debate) |

(Make into separate article) |

||

| Line 1: | Line 1: | ||

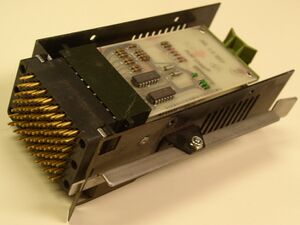

| − | + | [[Image:KIKLIOBusTerm.jpg|300px|right|thumb|KI10/KL10 I/O bus [[terminator]]]] | |

| + | |||

| + | The '''PDP-10 I/O Bus''', the [[PDP-10]] [[bus]] to which [[device controller]]s could be attached, was provided on the [[KA10]] and [[KI10]] models. It allowed [[peripheral]]s to [[interrupt]] the [[Central Processing Unit|CPU]], and supported [[programmed I/O]] (including block transfers); speeds of up to 200K transfers/second were possible on the KA10, and 350K transfers/second on the KIl0. | ||

| + | |||

| + | On the [[KL10]], an optional [[DIA20 In/Out Bus Controller]] could be attached, to provide a KA10/KI10 compatible I/O bus. | ||

| + | |||

| + | The DT01C I/O Bus Switch allowed a device to be switched between two different CPUs. | ||

| + | |||

| + | ==Physical form== | ||

| + | |||

| + | On the KA10, all the busses were physically instantiated as cables with a pair of [[DEC card form factor|dual]] width [[printed circuit board|PCBs]] at each end, which plugged into slots in a standard DEC [[backplane]]; these later became the CJ connectors. | ||

| + | |||

| + | On the KI10 and KL10, the I/O bus cables ended in a large QuickLatch connector; these connectors were on the CPU end of I/O bus cables of those machines. | ||

| + | |||

| + | ==See also== | ||

| + | |||

| + | * [[PDP-10 Memory Bus]] | ||

| + | |||

| + | ==External links== | ||

| + | |||

| + | * [http://www.bitsavers.org/pdf/dec/pdp10/KL10/EK-108OU-PD-002_KL10-Based_Physical_Description_Mar77.pdf EK-108OU-PD-002], "KL10-Based Physical Description" - has images of CJ dual card connectors and QuickLatch connectors, pp. 69-70 | ||

| + | |||

| + | [[Category: PDP-10s]] | ||

Latest revision as of 12:22, 23 October 2022

The PDP-10 I/O Bus, the PDP-10 bus to which device controllers could be attached, was provided on the KA10 and KI10 models. It allowed peripherals to interrupt the CPU, and supported programmed I/O (including block transfers); speeds of up to 200K transfers/second were possible on the KA10, and 350K transfers/second on the KIl0.

On the KL10, an optional DIA20 In/Out Bus Controller could be attached, to provide a KA10/KI10 compatible I/O bus.

The DT01C I/O Bus Switch allowed a device to be switched between two different CPUs.

Physical form

On the KA10, all the busses were physically instantiated as cables with a pair of dual width PCBs at each end, which plugged into slots in a standard DEC backplane; these later became the CJ connectors.

On the KI10 and KL10, the I/O bus cables ended in a large QuickLatch connector; these connectors were on the CPU end of I/O bus cables of those machines.

See also

External links

- EK-108OU-PD-002, "KL10-Based Physical Description" - has images of CJ dual card connectors and QuickLatch connectors, pp. 69-70