Difference between revisions of "MS11-P MOS memory"

(→External links: bitsavers does have the FMPS) |

m (Avoid dab) |

||

| Line 5: | Line 5: | ||

It has [[Error-correcting code|ECC]] which automagically corrects single-[[bit]] errors, <!--(at a slight penalty in [[access time|response time]] when an error occurs)--> and detects double-bit errors. On power-on, the system is frozen (via negation of the ACLO UNIBUS signal) while the entire memory is cleared, to prevent spurious ECC errors. For [[diagnostic]] purposes, the ECC can be disabled, and there are also means for the CPU to read/write the ECC bits directly. | It has [[Error-correcting code|ECC]] which automagically corrects single-[[bit]] errors, <!--(at a slight penalty in [[access time|response time]] when an error occurs)--> and detects double-bit errors. On power-on, the system is frozen (via negation of the ACLO UNIBUS signal) while the entire memory is cleared, to prevent spurious ECC errors. For [[diagnostic]] purposes, the ECC can be disabled, and there are also means for the CPU to read/write the ECC bits directly. | ||

| − | The [[access time]] is 490-535 nsec (read, typical/max; 215-230 nsec extra on error), 100-125 nsec (write); the [[cycle time]] is 680-750 nsec (read cycle) or 580-620 (write cycle). [[ | + | The [[access time]] is 490-535 nsec (read, typical/max; 215-230 nsec extra on error), 100-125 nsec (write); the [[cycle time]] is 680-750 nsec (read cycle) or 580-620 (write cycle). [[Memory refresh]] time is 675 nsec (typical; 725 nsec maximum), every 11.25-13.75 μsec. <!-- the time for a complete refresh pass is 12.5 μsec (typical), or 13.75 μsec (maximum) --> |

It is a [[DEC card form factor|hex-height]] card, the '''M8743''', and holds 1 Mbyte when fully populated with 64Kx1 DRAM [[integrated circuit|chips]]. The memory is arranged as 8 banks, each 16 data bits wide, with 6 additional bits for the ECC. | It is a [[DEC card form factor|hex-height]] card, the '''M8743''', and holds 1 Mbyte when fully populated with 64Kx1 DRAM [[integrated circuit|chips]]. The memory is arranged as 8 banks, each 16 data bits wide, with 6 additional bits for the ECC. | ||

Revision as of 19:18, 21 September 2022

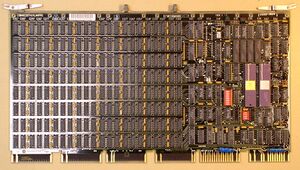

The MS11-P is a Extended UNIBUS MOS DRAM main memory card. As an EUB card, it can therefore only be plugged into the EUB slots on the PDP-11/24 or PDP-11/44 backplane.

It has ECC which automagically corrects single-bit errors, and detects double-bit errors. On power-on, the system is frozen (via negation of the ACLO UNIBUS signal) while the entire memory is cleared, to prevent spurious ECC errors. For diagnostic purposes, the ECC can be disabled, and there are also means for the CPU to read/write the ECC bits directly.

The access time is 490-535 nsec (read, typical/max; 215-230 nsec extra on error), 100-125 nsec (write); the cycle time is 680-750 nsec (read cycle) or 580-620 (write cycle). Memory refresh time is 675 nsec (typical; 725 nsec maximum), every 11.25-13.75 μsec.

It is a hex-height card, the M8743, and holds 1 Mbyte when fully populated with 64Kx1 DRAM chips. The memory is arranged as 8 banks, each 16 data bits wide, with 6 additional bits for the ECC.

It uses +5V only, unlike the earlier MS11-L and MS11-M MOS memories. The board has provision to use battery backup power to retain data during a power outage. Power requirements are 3.4-4.8A of +5V, and 2.0-2.8A of +5VBB.

External links

- MS11-P MOS Memory Technical Manual (EK-MS11P-TM-001)

- MS11-P Field Maintenance Print Set (MP01477)