|

|

| Line 1: |

Line 1: |

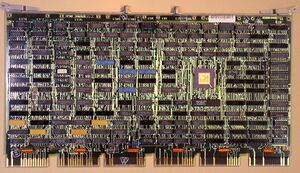

| | [[Image:KTJ11-B.jpg|300px|thumb|right|KTJ11-B board]] | | [[Image:KTJ11-B.jpg|300px|thumb|right|KTJ11-B board]] |

| | | | |

| − | The '''KTJ11-B UNIBUS adaptor''' is used with the [[KDJ11-B CPU|KDJ11-B]] and [[KDJ11-E CPU|KDJ11-E]] [[QBUS]] [[Central Processing Unit|CPU]] cards to add [[UNIBUS]] capability to systems built around those CPU cards, the [[PDP-11/84]] and [[PDP-11/94]] systems respectively. | + | The '''KTJ11-B UNIBUS adaptor''' is used with the [[KDJ11-B CPU|KDJ11-B]] and [[KDJ11-E CPU|KDJ11-E]] [[QBUS]] [[Central Processing Unit|CPU]] cards in the special [[KDJ11 PMI/UNIBUS backplane]] to add [[UNIBUS]] capability to systems built around those cards, the [[PDP-11/84]] and [[PDP-11/94]] systems respectively. It converts the native [[Private Memory Interconnect]] (PMI) [[bus]] supported by these |

| | | | |

| − | It is a [[DEC card form factor|hex-height]] board ('''M8191'''), and can only plug into a special [[backplane]], unique to those systems, which is wired to support it. | + | It is a [[DEC card form factor|hex-height]] board ('''M8191'''), and can only plug into the special [[backplane]], unique to those systems, which is wired to support it. |

| | | | |

| − | ==Backplane details== | + | ==Technical details== |

| | | | |

| − | The custom 12+1 slot backplane used by the KTJ11-B was half QBUS, and half UNIBUS (the 13th 'slot' is not a full slot, it only has a [[DEC edge connector contact identification|connector]] for one set of fingers). It has [[Private Memory Interconnect]] (PMI) bus slots at the top (for the CPU and [[main memory]] cards), a special slot in the middle for the KTJ11-B, and then UNIBUS slots. | + | The KTJ11-B contains a [cache]], to increase the efficiency of [[Direct Memory Access|DMA]] transfers on the UNIBUS; generally, two DMA red cycles on the UNIBUS result in a single PMI bus read operation. The cache contains 32 [[word]]-width entries, arranged into 4 independent 8-word sets; the KTJ11-B can thus handle 4 simultaneous DMA operations on the UNIBUS efficiently. |

| − | | |

| − | In detail, the backplane contains (in order) four [[DEC card form factor|quad-height]] slots, the first of which is the custom partial slot, and the others are PMI (technically [[QBUS#Variable address size|Q22]]/[[CD interconnect|CD]], although slightly modified from the normal form of that in this backplane, see below); they are used for (in order, from the front of the machine):

| |

| − | | |

| − | * the Machine Debug Monitor board (M7677); this slot is not numbered

| |

| − | * the CPU board; this is slot 1

| |

| − | * main memory board

| |

| − | * optional second main memory board

| |

| − | | |

| − | and nine hex-height slots, used for:

| |

| − | | |

| − | * KTJ11-B UNIBUS adapter, in slot 4

| |

| − | * four [[Small Peripheral Controller|SPC]] UNIBUS slots

| |

| − | * three [[Modified UNIBUS Device|MUD]] UNIBUS slots

| |

| − | * UNIBUS 'out' and quad SPC slot, in slot 12

| |

| − | | |

| − | Note that the PMI slots do not have the [[Private Memory Interconnect#CD interconnect details|bottom-up]] ordering of PMI-capable slots in a Q22/CD backplane, but are wired as a true bus, allowing the 'CPU, memory, memory' insertion ordering seen here.

| |

| − | | |

| − | Note also that in the normal configuration (see below for details), the QBUS [[bus grant line]]s are not routed through the memory slots, so if one of these slot is unused, there is no need for a [[M9047 grant continuity card]] in that slot.

| |

| − | | |

| − | As a further feature, on most UNIBUS backplanes, the 'NPG' ([[Direct Memory Access|DMA]] grant line) signal is carried across unused slots by wire jumpers on [[wire-wrap]] pins on the back side of the backplane; on the -11/84 backplane, they are brought out to a [[Dual Inline Package|DIP]] switch on the MDM module, for easier configuration changes.

| |

| − | | |

| − | Any UNIBUS slot which does not have a device installed in it, must have a [[bus grant|grant]] continuity card such as a [[G7273 grant continuity card|G7273]] placed in it.

| |

| − | | |

| − | ===Backplane layout===

| |

| − | | |

| − | Board locations are:

| |

| − | <!-- (as seen from the board insertion side of the backplane, not the wire-wrap pin side, as is common in [[Digital Equipment Corporation|DEC]] documentation) -->

| |

| − | | |

| − | {| class="wikitable"

| |

| − | ! !! colspan="6" | Connector

| |

| − | |-

| |

| − | ! Slot !! A !! B !! C !! D !! E !! F

| |

| − | |-

| |

| − | | 0 || colspan="4" style="text-align:center;" | M7677 MDM

| |

| − | |-

| |

| − | | 1 || colspan="4" style="text-align:center;" | M8190 or M8981 CPU

| |

| − | |-

| |

| − | | 2 || colspan="4" style="text-align:center;" | PMI memory

| |

| − | |-

| |

| − | | 3 || colspan="4" style="text-align:center;" | PMI memory

| |

| − | |-

| |

| − | | 4 || colspan="6" style="text-align:center;" | M8191 UBA

| |

| − | |-

| |

| − | | 5 || colspan="6" style="text-align:center;" | SPC device

| |

| − | |-

| |

| − | | 6 || colspan="6" style="text-align:center;" | SPC device

| |

| − | |-

| |

| − | | 7 || colspan="6" style="text-align:center;" | SPC device

| |

| − | |-

| |

| − | | 8 || colspan="6" style="text-align:center;" | SPC device

| |

| − | |-

| |

| − | | 9 || colspan="6" style="text-align:center;" | MUD device

| |

| − | |-

| |

| − | | 10 || colspan="6" style="text-align:center;" | MUD device

| |

| − | |-

| |

| − | | 11 || colspan="6" style="text-align:center;" | MUD device

| |

| − | |-

| |

| − | | 12 || colspan="2" style="text-align:center;" | UNIBUS Out || colspan="4" style="text-align:center;" | SPC

| |

| − | |}

| |

| − | | |

| − | ''Note:'' In an -11/94, there will usually be no PMI memory, but there will be an M9714 Alternate Power Source cards in connectors A-B of slot 2.

| |

| − | | |

| − | ===QBUS slots===

| |

| − | | |

| − | The two main memory slots can in fact be configured as regular Q22/CD QBUS slots, by removing two jumpers. EK-PDP84-TM-PR4 (PDP-11/84 Technical Manual) says (in section 2.1.14, "Backplane (H9277-A)", pg. 2-6):

| |

| − | | |

| − | : ''Bus signals BDMGI (pin AR2) and BIAKI (pin AM2) for slots 2 & 3 are jumpered on the front of the backplane.''

| |

| − | | |

| − | There are indeed two jumpers, W1 and W2 (in the upper right-hand corner, when facing the backplane from the board insertion side); the traces connected to them are on the surface, so it is possible to see where they go: one end runs to a trace connected from slot 1 to slot 2, and the other to a trace connected from slot 3 to slot 4; those connect to AM2 (BIAKI) and AN2 (BIAKO), and AR2 (BDMGI) and AS2 (BDMGO).

| |

| − | | |

| − | Thus, when the jumpers are in, the CPU's BIAKO/BDMGO pins are connected directly to the UNIBUS adapter's BIAKI/BDMGI pins; when they are out, those signals are routed through the two 'memory' slots, in the normal QBUS manner.

| |

| − | | |

| − | It therefore seems those two slots ''might'' be able to function as real QBUS slots. However, it is not clear that the CPU will 'do the right thing'; the UNIBUS adapter puts out a signal to let the CPU know that it is there, and the CPU may then expect to see only PMI-type DMA and [[interrupt]] cycles on the bus.

| |

| − | | |

| − | The DMA cycle ''might'' work, it all depends on what happens at step 8 (EK-KDJ1B-UG-001, pp. 7-6 to 7-9) when, instead of PBSY being asserted, BSYNC is asserted. The PMI ''memory'' will be fine (since in an -11/83, this kind of thing is expected)... but the ''CPU'', who knows. (The CPU would do the right thing in an -11/83, but the same board might not do the right thing here, since it 'knows' there is a UNIBUS adapter present.)

| |

| − | | |

| − | Interrupt cycles are more problematic; the assertion of the interrupt level on the BDAL lines (step 1a) will probably pass, but step 6 (assertion of BSACK) may be an issue, since the device will want to assert BRPLY instead (BSACK is not used in a QBUS interrupt), and the CPU may not do the right thing.

| |

| | | | |

| | ==External links== | | ==External links== |