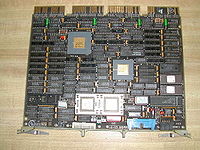

KDJ11-B CPU

The KDJ11-B CPU board (M8190) is the second-generation QBUS CPU card using the J-11 chip set of the PDP-11 (the first being the the KDJ11-A CPU). It is a quad-height board, and is used in the PDP-11/83 and PDP-11/84 systems.

Its principal improvement over the KDJ11-A is its support of the Private Memory Interconnect bus, a high-performance variant of the QBUS; it also supports the KTJ11-B UNIBUS adapter, a QBUS->UNIBUS adapter used in the PDP-11/84.

It also provides a built-in serial console, ROMs to contain diagnostic and bootstrap programs, and an EEPROM to contain configuration information.

Like the KDJ11-A, the -B also contains an 8K-byte write-through cache (set size 1, block size 1 16-bit word), protected by parity. The KDJ11-B additionally provides two sets of tag fields for each cache entry, so that the CPU and DMA from the QBUS can interact with the cache simultaneously. Cache control logic inspects DMA transfers and invalidates cache entries for memory words which are written to by a device.

Also like the KDJ11-A, it can also use the FPJ11 floating point accelerator chip to speed up the FP11 implementation in the J-11.

As far as is known, the various models of the KDJ11-B differ only in their speed (CPU and clock crystal) and whether or not they come with the FPJ11. DEC documentation refers to certain models being used in certain machines, but as far as is known, in fact any model will work in any machine.

Contents

Cache disable

There is a jumper that will disable the cache, for testing; it is jumper W20, on the lower right side of the board.

The 'KDJ11-B CPU Module User's Guide' (EK-KDJ1B-UG-001) has an erroneous entry regarding this jumper; it says (pg. 2-2, pg. 69 of the PDF) that "W20 installed" means "This condition is reserved". It should read "W20 removed - This condition is reserved".

Cache problems

The KDJ11-B cache implementation makes hard-to-diagnose stability problems a possibility. Below are some problems observed in a VCFed Forums repair thread from July 2024:

Intermittent CPU stoppage

During testing of Clearpoint QED1 and MSV11-J PMI memories, the system would randomly stop while running VMJAB0, the MSV11-J exerciser from XXDP. There was no error printout, no trap messages, no HALT to ODT, and the RUN lamp was out. The system came up from a restart and reported no errors in its self-tests. OKDAG0, the KDJ11-B cluster diagnostics, reported no errors, even with the switches set to 000300Q for extended cache tag and data RAM tests. After entering field service mode in VMJAB0 and disabling the J-11 cache, VMJAB0 would run without error or stoppage. After an extended run of VMJAB0, the system power-on diagnostics stopped with an error #162, which did not state that it was cache related, but should be -- #62 is a cache error, and for errors greater than 100, one subtracts 100 and uses the resulting number.

This problem was found to be a failing cache SRAM at position E10. The faulty chip was located through process of elimination, and was the fourth chip replaced. All other cache RAMs were OK.

Consistent Error 62 with printout

During burn-in testing of a repaired KDJ11-B from a large lot of scrap QBus boards, the KDJ11-B began stopping on every reset with a #62 cache error. The error could be bypassed with a CTRL+O 4 bypass. Once bypassed, the system could boot into XXDP, but OKDAG0 KDJ11-B cluster diagnostics reported no problems, even when run with the switches set to 000300Q for extended cache tag and data RAM tests.

This problem was found to be a failing cache SRAM at position E104, which is in the DMA tag RAM array. The faulty chip was located through process of elimination, and was the eleventh chip replaced. All other cache RAMs were OK.

Consistent Error 62 with lockup

During burn-in testing of a repaired KDJ11-B from a large lot of scrap QBus boards, the KDJ11-B began locking up on every reset with test #62 displayed on the lights. The system locked up hard and could not be HALTed to ODT without a reboot. No error was printed to the console. The EEPROM was moved to another KDJ11-B and configured to enter ODT on power-on, and skip all testing. This allowed booting into XXDP and running OKDAG0, KDJ11-B cluster diagnostics. With switches set to 000300Q for extended cache tag and data RAM tests, OKDAG0 would stop with the message:

ERROR IN RECORDING HITS THROUGH HITS/MISS REGISTER

Error printout indicated that the hit/miss shift register was not recording any hits, and remaining 000000Q regardless of the hit pattern attempting to be written to it.

The hit/miss register is implemented in the J-11 processor itself, but is fed signals from the DC350 gate array, which contains the cache control registers. These signals are combined through a 74S260 dual 5-input NOR gate at E22. The 74S260 had failed, and resolved the error upon replacement.

DC350 Gate Array Incompatibilities

During the diagnosis of a cache problem in this VCFed Forums repair thread from July 2024, it was discovered that DC350 gate arrays may not be interchangeable between board revisions. A LSI gold lid gate array from an early KDJ11-B with green top-side ECO was replaced with a silver lid gate array made in Japan from a later revision KDJ11-B. This resulted in a "mostly working" KDJ11-B, but OKDAG0 cluster diagnostics would randomly stop to ODT or loop endlessly without printout of pass completion or errors, and never prompted for user input for the KDJ11-B lamp register test. It is assumed that the DC350 revision was incompatible with the board revision.

See also

External links

- KDJ11-B CPU Module User's Guide (EK-KDJ1B-UG-001)

- KDJ11-B CPU System Maintenance (EK-247AA-MG-001)

- KDJ11-B Processor Specification

- 11/84 Field Maintenance Print Set (MP-02015-001) - Contains KDJ11-B Field Maintenance Print Set (MP-01969-01) on pp. 94-126