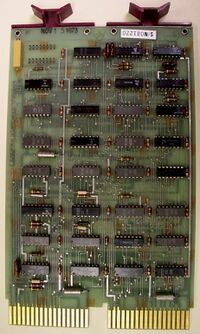

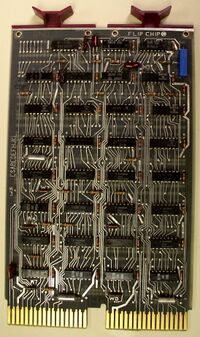

M7259 Parity Control Module

The M7259 Parity Control Module is an optional accessory for the parity versions of the MM11-L, MM11-U and MM11-W core memory main memory systems on the UNIBUS; it is needed for them to actually provide the parity protection.

It provides byte parity. Memory access time on read is increased by 125 nsec if parity is enabled. Cycle time on write is not affected if parity is enabled. On later revisions of the M7259, if an error occurs, an LED is illuminated.

The M7259 is a dual format card, which plus into a dedicated slot of the MF11-L/MM11-U/MM11-W backplane into which the associated memory unit(s) are plugged. Parity, and the M7259, is thus not supported for MM11-L/MM11-U units in a PDP-11/05 CPU backplane.

The M7259 requires slightly different backplane wiring for parity memory from non-parity (below). One M7850 can provide parity support to as many memory units as the backplane holds (3 for the MM11-L; 2 for the MM11-U).

Operation

The way the M7259 works is the same in all three memory systems that support it. An 'internal' version of the UNIBUS SSYN signal, SSYN INT BUS L, on pin BU1, connects together all memory units in the backplane, and the M7259.

On a read cycle, when the memory unit has put the data on the UNIBUS, it asserts that signal; on seeing it, the M7259 then generates and checks parity. (The two parity bits are transferred to the M7259 over 'private' lines on the backplane.) If it is correct, the M7259 asserts 'regular' SSYN on the UNIBUS; if incorrect, it signals a parity error to the CPU.

When the M7259 is in use, it drives the UNIBUS SSYN (on pin 1BU1) via pin BV2 in its slot; that pin is directly connected to the bus SSYN via a trace.

On backplanes used to hold the non-parity versions of memory units, a jumper connects the internal SSYN to the bus SSYN, from pin 1BU1 to 2BU1; this jumper should not be present for parity memory. (Note that therefore parity and non-parity memory cannot be mixed on the same backplane.)

Control and Status Register

The M7259 has a single register to control and monitor its operation. Its address may be set in the range 0772100-0772136 by a group of jumpers on the M7259. Its format is:

| ParErr | Unused | ErrAddr | Unused | WrWrong | Unused | SignalErr | |||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

Errors are not signaled to the CPU unless bit 0 is set. After an error, the ErrAddr field contains the highest-order address bits (A17-A11) of the location which produced the error. All bits can be written by the CPU; all except the Error Address are cleared by the INIT UNIBUS signal.

External links

- MM11-S, MF11-L, and MF11-LP core memory systems (DEC-11-HMFLA-C-D) - the M7259 is covered in Appendix A

- MF11-U/UP memory system engineering drawings - the M7259 is covered on pp. 7-40 of the PDF