KT11-B Technical Manual

As a Special Systems Option, the KT11-B does not have the usual DEC Technical Manual. This page attempts to provide at least the high-level portions of such a manual.

Note: KT11-B operation must be thoroughly understood (either from the KT11-B page above, or the Option Description manual) before trying to read this page. In particular, KT11-B external register names must be known, as well as the function of the CPU and device UNIBUSes, and also high-level internal entities such as the associative memories, and the scratchpad memory.

Further Note: This page is under construction. It is believed to be accurate, but the writer's understanding on the KT11-B circuity is not complete, and so it may contain errors.

Contents

- 1 High-Level Overview

- 2 Drawing Conventions

- 3 Signal Dictionary

- 4 Prints

- 5 Detailed logic description

- 5.1 Address Bus and Control Logic

- 5.2 State Control Logic

- 5.3 Scratchpad Input Mux

- 5.4 Associative Memory Control

- 5.5 Scratchpad and State Control Logic

- 5.6 Data Bus and Control Logic

- 5.7 Keys and Associative Memory

- 5.8 XP Option for KT11 Associative Memory Control

- 5.9 PGM Register

- 5.10 PGC Register

- 5.11 Timing Logic

- 5.12 Buffered Signals and Main Logic

- 5.13 Extended Associative Memory

- 5.14 KA11 to KT11 Interface

- 6 Construction

- 7 Card Information

High-Level Overview

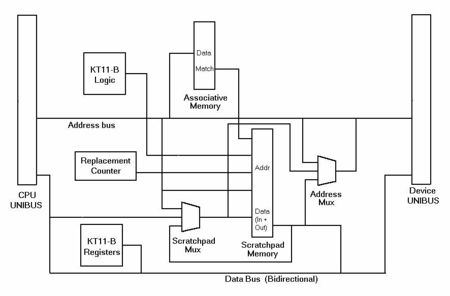

The heart of the KT11-B is the scratchpad memory, which is used to hold both cached page table entries, and also most of the KT11-B registers.

(Since the KT11-B does not contain any internal registers to which the CPU does not have access, the term 'register' hereinafter refers to any of the registers in the KT11-B visible to the CPU.)

The scratchpad has a built-in address multiplexor, so address lines from a variety of sources are all fed directly into it; see the "Keys and Associative Memory" section below, for details. A latching input data multiplexor is provided to select among data from a number of sources for storage in the scratchpad.

One of the possible inputs to that mux is the output of the scratchpad itself: since there is no latch on the output of the scratchpad, the ability to select its output, and then latch it, is sometimes used to hold data from the scratchpad for other users. (E.g. the comparator which checks to see whether cycles are in the 'Simple' part of the address space.)

A uni-directional address bus runs from the CPU's UNIBUS to the device UNIBUS; the KT11-B internals, such as the scratchpad, may also generate addresses (e.g. for loading page table entries). An address multiplexor for this bus can perform non-trivial selections (e.g. getting high address bits - i.e. physical page numbers - from scratchpad output, and low bits - i.e. addresses within a page - from the incoming address bus).

A bi-directional data bus connects to both UNIBUSes; the KT11-B may also source data to the CPU (e.g. when the CPU is reading KT11-B registers), or obtain data from either UNIBUS (e.g. for reading page table entries, or to intercept data the CPU is attempting to save to memory during a page fault).

The majority of the signals that control the operation of the buses, multiplexors, etc. are generated by random logic - a group of gates (and sometimes flip-flops as well); it is usually necessary to inspect the actual drawings to ascertain how any major data-handling item is controlled.

If the optional extended cache (holding an additional scratchpad memory, and an array of associative memories) is installed, it functions in much the same way as the base cache, except that since it does not hold any registers, its role is nowhere near as central as that of the main scratchpad.

States

A key part of KT11-B operation is a state composed of two parts, the 'X' or major part, and the 'Y' or minor part; the progression of this through the various states is the major control mechanism in the KT11-B.

Note that a state is only part of what controls the operation of the KT11-B; in many states, depending on control signal(s), differing actions may be taken, before the KT11-B moves on the same next state.

The X state counter (composed of a pair of D flops, with 4 AND gates with inverting inputs) creates individual major state outputs, signals 'XSRx' (x = 0-3).

The Y state counter is an M826 Flip Chip; its outputs are signals 'YSRx' (x = 0, 1 ,3, 7, 15, 14, 12, 8). (The odd sequence of minor state numbers, and the fact that they are not in numerical order, is confusing, but since that's what's on the prints, that nomenclature has to be used.)

The two groups of signals are combined into signals which indicate that the KT11-B is in that state, for each individual major/minor state, by NAND gates; inverters then provide non-inverted forms of each.

State Table

The following table shows the state transitions:

| State | Next State(s) | Comment |

|---|---|---|

| 0.0 | 0.8, 1.0 | Idle |

| 0.8 | 0.12 | Interrupt, Trap and Start User |

| 0.12 | 0.14 | |

| 0.14 | 0.15 | |

| 0.15 | 0.7A | |

| 0.7A | 0.3A | |

| 0.7B | 0.3B | Although the state names are identical to the preceding ones, this is shown on the state diagram as a separate state loop |

| 0.3A | 0.1A | |

| 0.3B | 0.1B | Window? |

| 0.1A | 0.0 | |

| 0.1B | 1.1 | Although the state name is identical to the preceding one, this is shown on the state diagram as a separate state loop |

| 1.0 | 1.1, 3.0 | |

| 1.1 | 1.3 | |

| 1.3 | 1.7, 3.3 | Exec-per-Process |

| 1.7 | 0.7B, 1.15 | |

| 1.15 | 1.14 | Page Violation? |

| 1.14 | 1.12 | |

| 1.12 | 0.12 | |

| 1.8 | 1.0 | |

| 2.0 | 0.0 | |

| 2.1 | 2.0, 2.3 | Shared Entry? |

| 2.3 | 2.7 | |

| 2.7 | 2.15 | |

| 2.15 | 2.14 | Page Violation? |

| 2.14 | 0.14 | |

| 2.12 | - | State does not exist |

| 2.8 | - | State does not exist |

| 3.0 | 2.0, 3.1, 3.8 | |

| 3.1 | 1.1, 2.1, 3.0 | |

| 3.3 | 3.1, 3.7A | |

| 3.7A | 1.7 | |

| 3.7B | 3.3 | Although the state name is identical to the preceding one, this is shown on the state diagram as a separate state loop |

| 3.15 | 3.7B | |

| 3.14 | 3.15 | |

| 3.12 | 3.14 | |

| 3.8 | 1.8, 3.12 |

This table is a transcription of the single-page one in the KT11-B Option Description; that diagram contains a number of labels, but it is not completely clear which states (or transitions) the labels apply to. Over time the hope is to check this table against the multi-page table in that document, and also better described what each state means/does.

Drawing Conventions

The drawings are somewhat easier to understand if the conventions used in the drawings are understood. Although no document lists them, they can be ascertained by study of the drawings.

Note that in the prints, the symbol '*' in a signal name means logical AND, and '+' means logical OR; this notation is used throughout the KT11-B prints.

Signal Names

Signal names as written in this drawing set usually start with 'Dxx', where 'xx' is related to the drawing number (given in the table below). (This is similar to the convention in the KA11 CPU drawings, where 'Kxx-y' means that the signal originates on page y of drawing xx.) Note that the 'Dxx' correspondence seems to sometimes be off by one; i.e. a signal tagged 'D04' can be found originating on drawing 05.

In signal names of the form 'XXX (yy)', 'yy' is a bit number (in standard PDP-11 order) in a register or bus. For signals which are provided in both asserted low and asserted high forms, one will see signal names of the form 'XXX (y)', where 'y' is 1 or 0. Note that sometimes these two notations are combined, and one can find signal names of the form 'XXX (yy) (z)'. Inverted (asserted low) signals are also sometimes shown as '-XXX'; this form is particularly common with composite signals (i.e. '-(xxx * yyy)').

The following specific signal names have the meaning given:

- Signals of the form 'x.y' are states, with 'x' being the major state, and 'y' being the minor state; the origin of all of them is on page D12.

- Signal names 'A (x)' are the internal address bus, and 'D (x)' are the data bus.

- Signal names starting with 'SP' refer to the scratchpad memory; SPIN is its input bus, and SPDA is its output bus.

- Signal names starting with 'AM' sometimes refer to the associative memory, but there are others, e.g. signals named 'ENB AMX' which control the address multiplexor.

- Signal names starting with 'DV' refer to the UNIBUS from the KT11-B to the devices and memory of the system.

- Signal names starting with 'CP' refer to the UNIBUS to the KT11-B from the KA11 CPU.

- Signal names starting with 'PGC' refer to the contents of the Control Status register.

- Signal names starting with 'PGM' refer to the contents of the Maintenance register.

Common Circuits

This circuit (first used in the KA11) is seen in several places in the KT11-B. It is almost always seen as an array of identical circuits, since it provides a 3-input multiplexor with latching capability, and it is used on data paths (usually 16 bits wide).

The latch is cleared by de-asserting the 'Latch' input; data from any of the three inputs (A, B, C) may then be selected for output, and potentially storage, by asserting the matching 'Gate' input. Asserting 'Latch' while an input is selected then stores the current output of the mux.

(Asserting more than one input simultaneously ORs the two inputs together; this capability is used in the KA11, but probably not here.)

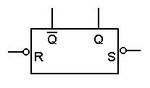

The prints use an unusual symbol for an SR flop, with the Q outputs at the top (shown here).

Some of the SR flops are variants with two 'set' inputs. Note that these are sometimes drawn with the two 'set' inputs on the left hand side, instead of the right; in this case, those inputs are being used as 'reset' inputs, and to compensate, the Q and -Q outputs are reversed; i.e. the usual Q output pin becomes the -Q output, and vice versa. (Since SR flops are symmetric with respect to the S/Q and R/-Q input/output pairs, this inversion is trivial.)

Signal Dictionary

These are main control signals, their meaning, and the drawing page (below) where they are generated. Listings of the form 'aaa(x) (y-z)' indicate that 'aaa' is a group of signals generated on page y-z, and this is the xth; similarly for 'bbb(w-x) (y-z)'. (Note that occasionally the drawings use the notation 'ccc(p:q) for a control signal which acts on bits p through q, or the AND of bits p through q.)

Note: A few of these are not actually generated as individual signals, only as composites. (E.g. "EXEC PER PROC" is only generated ANDed with "3.1". In that particular case, the drawing could have been modified to have an "EXEC PER PROC" output, but that would have been misleading, since that signal is not used elsewhere on its own.) Such cases are marked with a '+' on the signal name.

- A(0-17) (2-1): Internal address bus

- A CLK (7-1):

- AM CLK (5-2):

- AMOK (6-1): Associative memory matched

- AMXA(0-8) (2-2): Address mux output, high half

- AMXB(0-8) (2-2): Address mux output, low half

- CLC (7-1)

- CLK A (13-1): Maintenance clock pulse

- CLK AA (15-1):

- CLR B (2-1): Clear latch of B (high) half of address mux

- D(0-15) (7-2, 7-3): Internal data bus

- DST (5-2):

- ENB AMXA(0) (2-1): Select scratchpad output data for high address

- ENB AMXA(1) (2-1): Select scratchpad input mux data for high address

- ENB AMXA(2) (2-1): Select incoming address for high address

- ENB AMXB(0) (2-1): Select scratchpad output data for low address

- ENB AMXB(7:1) (2-1): Select scratchpad input mux data for low address

- ENB AMXB(8,0) (2-1): Select special data for low and high bits of address

- ENB AMXB(2) (2-1): Select incoming address for low address

- ENB C (7-1): Enable C0/C1 on device UNIBUS

- ENB CLK B (7-1):

- ENB CLK C (7-1):

- ENB CPD (7-1):

- ENB D (7-1):

- ENB SPOR(0) (6-1): Select scratchpad cache entry for read

- ENB SPOR(1) (6-1): Select scratchpad cache entry for replacement

- ENB SPOR(2) (6-1): Select scratchpad register for internal use

- ENB SPOR(3) (6-1): Select scratchpad register for UNIBUS access

- ENB XPOR(0-1, 3) (6-1): As above, but for extra scratchpad for optional cache extension

- +EXEC PER PROC (3-1):

- EXZE (5-1): Reference to Exec mode page 0

- FORCE TIMEOUT (15-1):

- INTRAP (5-1):

- KEY(0) (8-1): Writeable page

- KEY(1) (8-1): Public page

- KEY(2) (8-1): Resident page

- LONG (8-1): Address in Simple part

- LONGF (10-1): PGM(12)

- +LOOKUP (13-1):

- NORMAL (3-1):

- ODD ADD ERR (15-1):

- PAGE (5-1): Cycle with paging enabled?

- PAD SEL (5-1): Paging register selected?

- PASS (3-1): PGM(11)

- PGC(0), PGC(1) (11-1): Function (un-paged; normal; start user)

- PGC(1:0) (7-1): Start user

- PGC(4) (11-1): User mode

- PGC(7) (11-1): Interrupted User

- PGC(15:12) (11-1): Violation

- PGM(0-4) (10-1): Replacement Counter

- PGM(6) (10-1): Previous instruction User mode TRAP?

- PGM(7) (10-1): Previous instruction fetch Private?

- PGM(12) (10-1): Cycle to non-Simple part of addess space

- PGM(13) (10-1): Window access (phase 1)?

- PGM(14) (10-1): Window access (phase 0)?

- PGM(15) (10-1): Time out

- PKER (5-1): Paging error (write into a R/O page, etc)

- PKIV (5-1): Instruction violation - HALT, RESET, etc in User mode

- SP SEL (5-1):

- SPEN (6-1): Scratchpad output enable

- SPOR(2) (6-1): Register select

- SRC (5-2):

- uT (8-1):

- XSHL, XSHR (3-1): Controls major state transitions

- YSHL, YSHR (3-1): Controls minor state transitions

- WELF (10-1): PGM(13)

- WIND (5-1): Reference to Window register?

- WINF (10-1): PGM(14)

- WREND (7-2):

- WRITE (7:0) (6-1):

- WRITE (15:8) (6-1):

- XM CLK (5-2):

- XPEN (6-1): Optional scratchpad (for cache extension) output enable

The following signals are provided by the KA11:

- CLKT: ?

- DEST: In 'Destination' major state

- FETCH: In 'Fetch' major state

- ISR 7: Bit 7 of the current instruction

- ISR 12: Bit 12 of the current instruction

- JSR: Current instruction is 'JSR'

- RTI: Current instruction is 'RTI'

- RTS: Current instruction is 'RTS'

- SERVICE: In 'Service' major state

- SOURCE: In 'Source' major state

- TIME OUT:

- TRAP: Current instruction is 'TRAP'?

- TRAPS: ?

Prints

The Engineering Drawings for the KT11-B (7605071) include the following logic prints:

| Number | Page Count | Content |

|---|---|---|

| 2 | 2 | Address Bus and Control Logic |

| 3 | 1 | State Control Logic |

| 4 | 1 | SP Input Mux |

| 5 | 2 | Associative Memory Control |

| 6 | 1 | Scratch Pad and State Control Logic |

| 7 | 3 | Data Bus and Control Logic |

| 8 | 1 | Keys and Associative Memory |

| 9 | 1 | XP Option for KT11 Associative Memory Control |

| 10 | 1 | PGM Register |

| 11 | 1 | PGC Register |

| 12 | 1 | Timing Logic |

| 13 | 1 | Buffered Signals and Main Logic |

| 14 | 1 | Extended Associative Memory |

| 15 | 1 | KA11 to KT11 Interface |

| 17 | 1 | KT11-B Bus Connectors |

The KT11-B is not composed of discrete boards, but rather a large number of mostly small FLIP CHIPs, so the division into drawings, some of which are multi-sheet (as opposed to them all being single-sheet) is a bit arbitrary. It is probably intended to align the drawings with the high-level internal structure.

References to drawing pages are given as 'x-y', where 'x' the drawing number, and 'y' is the individual sheet.

Detailed logic description

This section covers each drawing in more detail, explaining what functions are found in each one. The term 'logic' below means a group of gates (and sometimes flops as well), often used to produce control signals.

Note: For describing which part of a print is being discussed, the terms 'left', 'center' and 'right' refer to the side-side axis, and 'top', 'middle' and 'bottom' refer to the up-down axis. Which axes 'center' and 'middle' refer to can be remembered by the observation that 'center' is usually used in a side-side context, not an up-down one.

Address Bus and Control Logic

The first sheet contains, on the left, buffering between the address lines of the CPU's UNIBUS, and the internal address bus; and in the center and right, logic which generates control signals for the address mux (on the next page).

The left of the second sheet contains an address latching mux (see above for the implementation), divided into high and low 9-bit halves, which may be controlled separately (for page and byte-within-page), and which separately select between:

- Scratch-pad data output (9 bits wide, repeated in the low and high halves)

- Scratch-pad data input (18 bits wide, with the low and high halves swapped - although note that that data source is only 16 bits wide: so the low bit in the low half is zero - presumably because only word addresses are used; and the high bit in the low half is a synthetic signal)

- The internal address bus

The right half of the second sheet contains drivers for the address lines of the device UNIBUS, sourced from the above mux.

State Control Logic

This drawing contains logic which generates two state change control signals for each of the major and minor states (XSHL, XSHR, YSHL, YSHR).

Scratchpad Input Mux

At the top, a 16-bit wide latching mux (see above) which provides the input to the scratchpad memory. The three inputs are:

- The internal address bus

- The internal data bus

- Scratchpad data output

At the bottom is logic which generates the selection control signals for that mux.

Associative Memory Control

The first sheet contains a number of different logical units: the top left contains logic which indicates that the CPU is 'executing a TRAP instruction'?/'in a trap sequence'?; the top right contains logic to recognize references to KT11-B internal registers; and the bottom right contains logic to generate several control signals.

The bottom left contains logic to detect illegal instructions in User mode (HALT, WAIT and RESET), and non-'entry' instruction when transferring to a private page. The column of three 4-input NAND gates recognize the 'entry' instruction, HALT/WAIT, and RESET, respectively; the first is then combined wirh other signals (PGC(7)(0) is probably a type for PGM(7)(0)), before all three are ORed together, and then ANDed with signals indicating the KA11 is in (instruction) 'Fetch' major state, and the KT11-B is in 'User' mode, to generate the IV error signal.

The second sheet also contains a number of different logical units: the right side contains logic to load individual associative memories; the bottom left contains logic to generate the binary-coded identification of the scratchpad memory entry corresponding to a associative memory which matched (used to read that entry out of the scratchpad); the center bottom contains logic to indicate an associative memory match.

Scratchpad and State Control Logic

Logic which controls the scratchpad memory: the center top and entire right side contain logic which (apparently) indicates which register (stored in the scratchpad) the KT11-B itself needs access to; the center bottom contains logic which indicates which set of scratchpad address inputs (out of four, see the "Keys and Associative Memory" section) are to be used ; the left bottom performs the same function for the scratchpad in the optional extended cache.

Data Bus and Control Logic

The first sheet contains logic to create various control signals.

The far left of the second sheet contains input buffers (from the CPU's UNIBUS) for various bus control signals; the center left contains the drivers for data lines of the device UNIBUS, which are fed from the (buffered) data lines of the CPU's UNIBUS; the right contains half of a multiplexor (built from NAND gates connected in a wired-OR network) which drives the data lines of the CPU's UNIBUS, for which the inputs are:

- The data lines of the device UNIBUS (through a set of receivers, which also generate the internal data bus)

- Scratchpad data output

- The KT11-B Control and Maintenance registers

The left and center of the third sheet contains the other half of the data mux; the right shows the KW11-L Line Time Clock card.

Keys and Associative Memory

The left side shows the scratchpad memory; note that the register number input select lines (top group, left side of the block) select one of four sets of register number input lines (also on the left). From the top, they are:

- The binary-coded number of the associative memory that matched - note that the high bit is tied high, indicating the cache page table entries are stored in the top half of the scratchpad

- Replacement counter (from the KTMR); note that the lowest value this can have is 010, so that it always addresses cache entries, which are stored in the top 010 locations

- A set of signals which apparently indicate which register the KT11-B needs to be able to store - note that the high bit here is tied low, indicating they are stored in the bottom half of the scratchpad

- The low bits of the internal address bus (likely for register read-out)

The top center shows the associative memories; note that the only inputs to each are the 7 high bits of the internal address bus, and the Exec/User mode bit; the associative memory must be loaded from the internal address bus early during a cycle which provokes a cache replacement.

The top right shows a comparator used for the division of the Exec and User address spaces into two kinds of pages; the bottom right is the counter?/shift register? which generates the minor state.

The bottom center is a 3-bit wide latching mux which holds protection key information for the current memory cycle. The three inputs are:

- A signal indicating a reference to Exec mode page 0 (replicated to all three key bits), used to generate a synthetic 07 key for Exec page 0 (which does not have a page table entry)

- 3 bits from the device UNIBUS (for page table entries loaded from memory)

- 3 bits from the scratchpad (for cached page table entries)

XP Option for KT11 Associative Memory Control

This contains logic to control the optional cache entries: the left and center contain gates to control loading of associative memories; the right contains logic to generate the binary-coded identification of the entry in the optional scratchpad memory (used with the extended cache) corresponding to a associative memory which matched.

PGM Register

The KT11-B's Maintenance register: the center top is the replacement counter; the rest of the page is logic (including S/R flops) to generate the currently un-documented other bits in the Maintenance register - bits 6, 7, 11, 12, 13, 14, 15. (The Option Description indicates - Section 3.3.2.6 - that there are 5 bits, but the drawings show 7.) Note than many of these bits are actually used elsewhere in the KT11-B during normal operation, they are not purely diagnostic.

The top right is logic to record that the instruction is a TRAP in User mode; it includes a modified 'gated D latch' (with addition inputs to the SR latch which is its second stage). The middle and lower right is logic (again including a 'gated D latch') that records if a cycle is to the non-Simple part of the address space; the middle center is a delayed copy of that. The bottom center holds logic to record that the CPU reported a timeout, and logic to record a cycle to the Window register; the lower left corner contains a delayed copy of that. The middle left is logic (again including a 'gated D latch') that records if a fetch is to a Private page.

PGC Register

The KT11-B's Control and Status register - S/R flops to store the bits, and logic to control setting and clearing them: in the upper right, the Source and Destination bits; in the center and lower right, the five Violation bits; in the upper left and center, the two Function bits; in the left and center middle, the User and Interrupted User bits, respectively.

Timing Logic

Main article: KT11-B Major State circuitry

The top and lower right contain gates which combine major and minor state lines into signals for each individual state.

The lower left contains the 2-bit counter (built out of two D flops, and associated circuitry) which produces the major state; and also logic to produce major state signals. Note that the two flops (and their input circuitry) don't form a straight binary counter, but rather a Gray code counter. So, a sequence of XSHL pulses will generate the following major state sequence:

00, 10, 11, 01, 00

and XSHR will produce:

00, 01, 11, 10, 00

Buffered Signals and Main Logic

The left side shows the W130 Maintenance Card; the top left and center contain buffering for various internal signals; the right contains buffering for the high 9 bits (i.e. the page number) of the internal address bus.

Extended Associative Memory

On the left, the scratchpad memory for the optional 16-entry page table cache extension (to 24 entries total), with the possible register number inputs:

- The binary-coded number of the extended associative memory that matched

- Replacement counter (from the KTMR)

- The low bits of the internal address bus (likely for register read-out)

Note that the fourth set of address inputs to the scratchpad are unused (note the selector line for that set of inputs is tied low).

The center and right are the associative memories for the extended cache.

KA11 to KT11 Interface

In addition to the interface cable, this sheet also shows the synthesis of a number of signals which are passed across the interface.

Note that the gates on the left are actually physically in the KA11 (an additional M135 hex NAND card is plugged into slot B08 of the KA11's backplane).

In addition to logic in the KT11, the right side also shows buffers for signals coming from, or going to, the interface cable.

Construction

As mentioned, the KT11-B is constructed out of a large number of smaller FLIP CHIPs, plugged into a custom-wired backplane.

Module Counts

The module type usage counts are:

| Type | Function | Count | Comment |

|---|---|---|---|

| M111 | 16 x Inverters | 10 | |

| M112 | 10 x 2-input NOR | 5 | |

| M116 | 6 x 4-input NOR | 10 | |

| M133 | 10 x 2-input NAND | 24 | |

| M135 | 8 x 3-input NAND | 6 | |

| M139 | 3 x 8-input NAND | 1 | |

| M167 | Magnitude comparator | 1 | |

| M203 | 8 x R/S flip flops | 1 | |

| M206 | 6 x D flip flops | 1 | |

| M207 | 6 x J/K flip flops | 1 | |

| M225 | Scratchpad memory | 1 | 2 for 24 cache entries |

| M240 | R/S flip flop | 1 | |

| M244 | 6 x quad-2-input-AND/OR gates | 6 | Used as latched multiplexors (see above) |

| M259 | Associative memory | 4 | 12 for 24 cache entries |

| M602 | 2 x Pulse amplifier | 1 | |

| M611 | 14 x Power inverter | 3 | |

| M627 | 6 x NAND amplifier | 7 | |

| M721 | UNIBUS transceiver | 4 | |

| M783 | 12 x UNIBUS NAND transmitters | 6 | |

| M784 | 16 x UNIBUS inverter receivers | 2 | |

| M826 | Clock/shift register | 1 |

The counts are from the list in the "KT11-B Option Description" document; they have been cross-checked against the 'Module Utilization' sheet from the KT11-B Engineering Drawings, and also the module location chart (below) and all known variances have been sorted out.

Module Locations

The following table, drawn from the 'Module Utilization' sheet from the KT11-B Engineering Drawings, gives the location of the various modules in the backplane:

| Slot | A | B | C | D |

|---|---|---|---|---|

| 01 | UNIBUS In | M259 | M133 | |

| 02 | M930 | M259 | M133 | |

| 03 | UNIBUS Out | M259 | M133 | |

| 04 | M930 | M259 | ||

| 05 | M721 | M721 | M259% | |

| 06 | M721 | M721 | M259% | |

| 07 | M783 | M784 | M259% | |

| 08 | M783 | M784 | M259% | M133 |

| 09 | M783 | M787 $ | M259% | M133 |

| 10 | M783 | M244 | M259% | M133 |

| 11 | M783 | M244 | M259% | M133 |

| 12 | M783 | M244 | M259% | M903 @ |

| 13 | M826 | M244 | M627 | M111 |

| 14 | W130 $ | M244 | M627 | M133 |

| 15 | M116 | M244 | M627 | M133 |

| 16 | M225 | M627 | M133 | |

| 17 | M225% | M111 | M133 | |

| 18 | M116 | M112 | M627 | M133 |

| 19 | M116 | M112 | M627 | M133 |

| 20 | M116 | M112 | M627 | M133 |

| 21 | M116 | M112 | M133 | |

| 22 | M116 | M112 | M133 | |

| 23 | M116 | M602 | M133 | |

| 24 | M116 | M135 | M133 | |

| 25 | M116 | M135 | M611 | M133 |

| 26 | M116 | M135 | M611 | M133 |

| 27 | M203 | M135 | M111 | M133 |

| 28 | M206 | M135 | M111 | M133 |

| 29 | M207 | M135 | M611 | M133 |

| 30 | M240 | M133 | M111 | M111 |

| 31 | M139 | M111 | M111 | |

| 32 | M167 | M111 | M111 | |

- % = Optional

- $ = Not part of KT11-B

- @ = Cable

Questionable entries (since the table is hand-written, and hard to read in places because of poor-quality duplication from the originals) have been cross-checked against the prints, and all known uncertainties have been cleared up.

Card Information

The drawings contain a number of different FLIP CHIPs as blocks, without showing individual details; information about them is given here. (Internal details of the M259 and M826 are currently unknown; unless examples are found, so that they can be reverse engineered, they will probably remain so.)

M167

Shown on page 8-1, this is a 8-bit comparator; see here for details.

M203

Shown on pages 7-1, 10-1 and 11-1, although not as as a single block, but rather individual units, this contains eight R/S flip flops; see here for details.

M225

Shown on pages 8-1 and 14-1, this is a 16x16-bit scratchpad memory; see here for details.

Pin AN1 is a control input of some sort, but it is not yet clear what it does. It is possible that it is some sort of 'output enable', for use in cases where the optional second scratchpad memory is installed, since the two feed the same output bus.

M240

Shown on pages 10-1 and 11-1, although not as as a single block, but rather individual units, this contains six R/S flip flops; see here for details.

M259

Shown on pages 8-1 and 14-1, this is a dual 8-bit associative memory.

M602

Shown on pages 6-1 and 13-1, although not as as a single block, but rather individual units, this is a dual pulse amplifier; see here for details.

M787

Shown on page 7-3, this is actually not a part of the KT11-B; rather, it is the KW11-L Line Time Clock, which must reside in the KT11-B's backplane.

M826

Shown on page 8-1, this is a clock with counter?/shift-register?

W180

Shown on page 13-1, this is actually not a part of the KT11-B; rather, it is the Maintenance Card, which must plug into the KT11-B's backplane.