Difference between revisions of "MM11-U core memory"

(clarify that 11/05 CPU backplane version cannot support parity operation) |

(boards shared with MG10) |

||

| (8 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

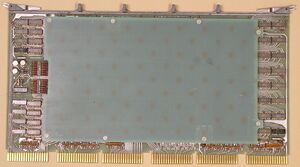

| − | + | [[Image:H217DCoreStack.jpg |300px|thumb|right|H217-D core stack module]] | |

| − | + | The '''MM11-U''' was a popular, and fairly common, 32 Kbyte [[core memory|core]] [[main memory]] system for the early [[PDP-11]] [[UNIBUS]] machines. An MM11-U was composed of a four board set: | |

| − | |||

| − | |||

| − | |||

| − | + | * G114 - [[DEC card form factor|hex-width]] sense/inhibit module | |

| + | * G235 - hex-width XY Drive, current source, decode module | ||

| + | * H217-D - hex-width core stack | ||

| + | * M7293/M8293 - quad-width timing and control module | ||

| − | The | + | (The difference between the M7293 and M8293 is unknown; later documentation always refers to the M8293 only, and it is the one usually seen.) |

| − | The '''MF11-U''' was a | + | The MM11-U/UP usually required a custom nine-slot [[backplane]] ([[DEC part number]] 54-10345 or 70-09295), although some [[Central Processing Unit|CPU]]'s (e.g. the [[PDP-11/05]]) had processor backplanes wired to hold an MM11-U set, as well as the CPU set. |

| + | |||

| + | The '''MF11-U''' was a backplane plus a single MM11-U board set; the backplane has room for one more MM11-U board set. | ||

| + | |||

| + | There was also a [[parity]]-capable variant, the '''MM11-UP''', which added an dual-width [[M7259 Parity Control Module]], and substituted an H217-C (with two more bits per word - for byte parity) for the H217-D. | ||

| + | It was only available for the MF11-U, not in the CPUs, since it required an extra slot for the M7259 parity controller. | ||

| + | |||

| + | The board set of the MM11-U (less the M8293) is also used in the [[MJ11 memory system]], and (with the 19-bit wide H217-B variant of the core stack) in the [[MG10 core memory]]. | ||

| + | |||

| + | ==Module chart== | ||

| + | |||

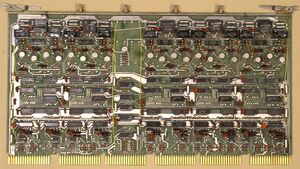

| + | [[Image:G114SenseInhibit.jpg|300px|thumb|right|G114 sense/inhibit module]] | ||

| + | |||

| + | The board organization in the MF11-U backplanes is (viewed from the module side of the backplane): | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! !! colspan="6" | Connector | ||

| + | |- | ||

| + | ! Slot !! A !! B !! C !! D !! E !! F | ||

| + | |- | ||

| + | | 1 || colspan="2" | UNIBUS In || colspan="4" | M8293 Timing + Control | ||

| + | |- | ||

| + | | 2 || colspan="2" | M7259 Parity Controller || colspan="4" | ''Unused'' | ||

| + | |- | ||

| + | | 3 || colspan="6" style="text-align:center;" | G114 Sense/Inhibit | ||

| + | |- | ||

| + | | 4 || colspan="6" style="text-align:center;" | H217C/D Core stack | ||

| + | |- | ||

| + | | 5 || colspan="6" style="text-align:center;" | G235 X/Y Driver | ||

| + | |- | ||

| + | | 6 || colspan="6" style="text-align:center;" | G235 X/Y Driver | ||

| + | |- | ||

| + | | 7 || colspan="6" style="text-align:center;" | H217C/D Core stack | ||

| + | |- | ||

| + | | 8 || colspan="6" style="text-align:center;" | G114 Sense/Inhibit | ||

| + | |- | ||

| + | | 9 || colspan="2" | UNIBUS Out || colspan="4" | M8293 Timing + Control | ||

| + | |} | ||

| + | |||

| + | The first MM11-U set normally goes in slots 1/3/4/5; when the second MM11-U set was added, it was normally installed in slots 6/7/8/9; the order could be reversed, though. | ||

==Parity and non-parity backplane configuration== | ==Parity and non-parity backplane configuration== | ||

| Line 16: | Line 55: | ||

Installing an MM11-U (non-parity) module set in an MF11-UP backplane will cause the machine to hang when that memory is referenced. | Installing an MM11-U (non-parity) module set in an MF11-UP backplane will cause the machine to hang when that memory is referenced. | ||

| − | This is because during parity operation, the SSYN signal is routed through the M7259 | + | This is because during parity operation, the SSYN signal is routed through the M7259 parity controller board, and that only issues the SSYN once it has checked that the parity is OK. On non-parity installations, the 'proto-SSYN' from the rest of the memory is just hard-wired straight to the output to the UNIBUS. |

That requires a jumper on the backplane for non-parity memory: it runs from pin B1U1 to B2U1. This jumper should not be present for parity memory. Note that therefore parity and non-parity memory cannot be mixed on the same backplane. | That requires a jumper on the backplane for non-parity memory: it runs from pin B1U1 to B2U1. This jumper should not be present for parity memory. Note that therefore parity and non-parity memory cannot be mixed on the same backplane. | ||

==G235 jumpers== | ==G235 jumpers== | ||

| + | |||

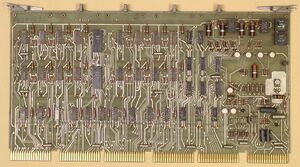

| + | [[Image:G235XYDrive.jpg|300px|thumb|right|G235 XY Drive, current source, decode module]] | ||

The MM11-U manual (EK-MF11U-MM-003) describes (pg. 3-12) a set of jumpers (W5-W7) on the G235 card (X and Y selection line current generators - those for the inhibit lines are on the G114) which adjust the bias current for the selection line generators. It goes on to say: | The MM11-U manual (EK-MF11U-MM-003) describes (pg. 3-12) a set of jumpers (W5-W7) on the G235 card (X and Y selection line current generators - those for the inhibit lines are on the G114) which adjust the bias current for the selection line generators. It goes on to say: | ||

| Line 34: | Line 75: | ||

There ''is'' a test to know if the bias current is properly adjusted (see Section 5.3.4, "Drive Current Checks"), and also for the strobe delay (Section 5.3.3, "Sense Strobe Delay Checks"). So in theory, if a G235 card fails one of these tests, it should be possible to change the smallest value jumper, and see if that made things worse or better; and then loop. | There ''is'' a test to know if the bias current is properly adjusted (see Section 5.3.4, "Drive Current Checks"), and also for the strobe delay (Section 5.3.3, "Sense Strobe Delay Checks"). So in theory, if a G235 card fails one of these tests, it should be possible to change the smallest value jumper, and see if that made things worse or better; and then loop. | ||

| − | ==Board inter-changeability== | + | ===Board inter-changeability=== |

There was some concern that these boards were 'tuned' to be part of a set. E.g. one of the components, in the circuit that the W5-W7 jumpers are part of, is a thermistor on the core stack board (H217). It is not clear if the jumpers are just for dealing with component variations on the G235 board, or if they also include variation elsewhere. In other words, there was a possibility that MM11-U's came as tuned board sets, which should not be 'mixed and matched'. | There was some concern that these boards were 'tuned' to be part of a set. E.g. one of the components, in the circuit that the W5-W7 jumpers are part of, is a thermistor on the core stack board (H217). It is not clear if the jumpers are just for dealing with component variations on the G235 board, or if they also include variation elsewhere. In other words, there was a possibility that MM11-U's came as tuned board sets, which should not be 'mixed and matched'. | ||

| Line 41: | Line 82: | ||

Thus, any 'mixing and matching' that has happened to these boards if they were removed from their machines has probably not caused any problems. | Thus, any 'mixing and matching' that has happened to these boards if they were removed from their machines has probably not caused any problems. | ||

| + | |||

| + | ==See also== | ||

| + | |||

| + | * [[UNIBUS memories]] | ||

| + | |||

| + | ==External links== | ||

| + | |||

| + | * [http://www.bitsavers.org/www.computer.museum.uq.edu.au/pdf/DEC-11-HMFMA-B-D%20MF11-U-UP%20Core%20Memory%20System%20Maintenance%20Manual.pdf MF11-U/UP core memory system maintenance manual] (DEC-11-HMFMA-B-D) | ||

| + | * [http://www.bitsavers.org/www.computer.museum.uq.edu.au/pdf/EK-MF11U-MM-003%20MF11-U&UP%20Core%20Memory%20System%20Maintenance%20Manual.pdf MF11-U/UP core memory system maintenance manual] (EK-MF11U-MM-003) | ||

| + | * [http://www.bitsavers.org/pdf/dec/pdp11/memory/MF11-U_UP_Memory_System_Engineering_Drawings_RevF_Jan76.pdf MF11-U/UP memory system engineering drawings] | ||

| + | |||

| + | [[Category: UNIBUS Memories]] | ||

Latest revision as of 04:53, 22 October 2021

The MM11-U was a popular, and fairly common, 32 Kbyte core main memory system for the early PDP-11 UNIBUS machines. An MM11-U was composed of a four board set:

- G114 - hex-width sense/inhibit module

- G235 - hex-width XY Drive, current source, decode module

- H217-D - hex-width core stack

- M7293/M8293 - quad-width timing and control module

(The difference between the M7293 and M8293 is unknown; later documentation always refers to the M8293 only, and it is the one usually seen.)

The MM11-U/UP usually required a custom nine-slot backplane (DEC part number 54-10345 or 70-09295), although some CPU's (e.g. the PDP-11/05) had processor backplanes wired to hold an MM11-U set, as well as the CPU set.

The MF11-U was a backplane plus a single MM11-U board set; the backplane has room for one more MM11-U board set.

There was also a parity-capable variant, the MM11-UP, which added an dual-width M7259 Parity Control Module, and substituted an H217-C (with two more bits per word - for byte parity) for the H217-D. It was only available for the MF11-U, not in the CPUs, since it required an extra slot for the M7259 parity controller.

The board set of the MM11-U (less the M8293) is also used in the MJ11 memory system, and (with the 19-bit wide H217-B variant of the core stack) in the MG10 core memory.

Contents

Module chart

The board organization in the MF11-U backplanes is (viewed from the module side of the backplane):

| Connector | ||||||

|---|---|---|---|---|---|---|

| Slot | A | B | C | D | E | F |

| 1 | UNIBUS In | M8293 Timing + Control | ||||

| 2 | M7259 Parity Controller | Unused | ||||

| 3 | G114 Sense/Inhibit | |||||

| 4 | H217C/D Core stack | |||||

| 5 | G235 X/Y Driver | |||||

| 6 | G235 X/Y Driver | |||||

| 7 | H217C/D Core stack | |||||

| 8 | G114 Sense/Inhibit | |||||

| 9 | UNIBUS Out | M8293 Timing + Control | ||||

The first MM11-U set normally goes in slots 1/3/4/5; when the second MM11-U set was added, it was normally installed in slots 6/7/8/9; the order could be reversed, though.

Parity and non-parity backplane configuration

Installing an MM11-U (non-parity) module set in an MF11-UP backplane will cause the machine to hang when that memory is referenced.

This is because during parity operation, the SSYN signal is routed through the M7259 parity controller board, and that only issues the SSYN once it has checked that the parity is OK. On non-parity installations, the 'proto-SSYN' from the rest of the memory is just hard-wired straight to the output to the UNIBUS.

That requires a jumper on the backplane for non-parity memory: it runs from pin B1U1 to B2U1. This jumper should not be present for parity memory. Note that therefore parity and non-parity memory cannot be mixed on the same backplane.

G235 jumpers

The MM11-U manual (EK-MF11U-MM-003) describes (pg. 3-12) a set of jumpers (W5-W7) on the G235 card (X and Y selection line current generators - those for the inhibit lines are on the G114) which adjust the bias current for the selection line generators. It goes on to say:

- Jumpers W5-W7 are factory cut to adjust the bias current to its optimal value and they should not be changed.

There is apparently a similar adjustment for the timing of the sense strobe.

The original procedure for setting those jumpers is likely lost, as it is probably only in some internal DEC documentation. The manual says (Section 5.4.2, "Sense Strobe Delay and Drive Current Adjustments"):

- Correction of any failure in either the sense strobe delay or drive current circuits on the G235 module that would require reconfiguration of the jumpers within these circuits should not attempted in the field. Replace the faulty module with a spare G235 module and return the faulty G235 module to the factor for repair.

There is a test to know if the bias current is properly adjusted (see Section 5.3.4, "Drive Current Checks"), and also for the strobe delay (Section 5.3.3, "Sense Strobe Delay Checks"). So in theory, if a G235 card fails one of these tests, it should be possible to change the smallest value jumper, and see if that made things worse or better; and then loop.

Board inter-changeability

There was some concern that these boards were 'tuned' to be part of a set. E.g. one of the components, in the circuit that the W5-W7 jumpers are part of, is a thermistor on the core stack board (H217). It is not clear if the jumpers are just for dealing with component variations on the G235 board, or if they also include variation elsewhere. In other words, there was a possibility that MM11-U's came as tuned board sets, which should not be 'mixed and matched'.

However, the second block of text above alleviated that concern: apparently one can replace one G235 with another, without swapping out all the boards in the set.

Thus, any 'mixing and matching' that has happened to these boards if they were removed from their machines has probably not caused any problems.

See also

External links

- MF11-U/UP core memory system maintenance manual (DEC-11-HMFMA-B-D)

- MF11-U/UP core memory system maintenance manual (EK-MF11U-MM-003)

- MF11-U/UP memory system engineering drawings