Difference between revisions of "PDP-8/I"

m (→Images: +Another image) |

(+implementation details) |

||

| Line 22: | Line 22: | ||

}} | }} | ||

| − | The '''PDP-8/I''' was introduced in 1968 as the successor to the [[PDP-8]]. It was constructed out of [[Transistor-transistor logic|TTL]] [[integrated circuit|ICs]] on M-class [[FLIP CHIP]]s | + | The '''PDP-8/I''' was introduced in 1968 as the successor to the [[PDP-8]]. It was constructed out of [[Transistor-transistor logic|TTL]] [[integrated circuit|ICs]] on M-class [[FLIP CHIP]]s - mostly early [[DEC card form factor|standard-length single-height]] (width) ones, with a few dual-height. It was the first [[Digital Equipment Corporation|DEC]] computer to be built using ICs. |

Options included: | Options included: | ||

| Line 42: | Line 42: | ||

[[Image:PDP-8'I HoppeLighted.jpg|left|thumb|400px|PDP-8/I of the Göttingen Computer Club in Göttingen, Germany]] | [[Image:PDP-8'I HoppeLighted.jpg|left|thumb|400px|PDP-8/I of the Göttingen Computer Club in Göttingen, Germany]] | ||

| + | |||

| + | <br clear=all> | ||

[[:File:PDP-8'I ComputerCabinettGöttingen.jpg|Another image]] | [[:File:PDP-8'I ComputerCabinettGöttingen.jpg|Another image]] | ||

| Line 47: | Line 49: | ||

==External links== | ==External links== | ||

| − | * [http://www.bitsavers.org/pdf/dec/pdp8i PDP-8/I] - Original PDP-8/I documents | + | * [http://www.bitsavers.org/pdf/dec/pdp8/pdp8i PDP-8/I] - Original PDP-8/I documents |

{{Nav PDP-8}} | {{Nav PDP-8}} | ||

[[Category: PDP-8s]] | [[Category: PDP-8s]] | ||

Revision as of 15:34, 19 April 2022

| PDP-8/I | |

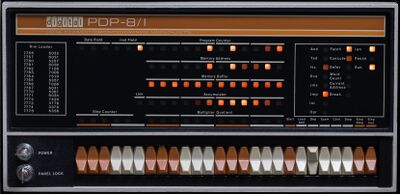

PDP-8/I front panel | |

| Year Introduced: | 1968 |

|---|---|

| Form Factor: | minicomputer |

| Word Size: | 12 |

| Logic Type: | TTL |

| Design Type: | clocked random logic |

| Clock Speed: | 333KHz |

| Memory Speed: | 1.5 μseconds |

| Physical Address Size: | 32KW (requires optional MC8/I) |

| Virtual Address Size: | 4KW |

| Memory Management: | bank selection, CPU mode |

| Bus Architecture: | negative I/O bus |

| Operating System: | TSS/8. Disk Monitor System |

| Predecessor(s): | PDP-8 |

| Successor(s): | PDP-8/E |

The PDP-8/I was introduced in 1968 as the successor to the PDP-8. It was constructed out of TTL ICs on M-class FLIP CHIPs - mostly early standard-length single-height (width) ones, with a few dual-height. It was the first DEC computer to be built using ICs.

Options included:

- KA8/IB Positive I/O Bus Interface, to allow use of newer PDP-8 devices

- DW08A Negative I/O Bus Conversion Option (on systems with a KA8/I, allows use of older PDP-8 devices)

- DW08B Positive I/O Bus Conversion Option (on systems without a KA8/I, allows use of newer PDP-8 devices)

- DW8-E OMNIBUS Interface (converts the positive bus of an 8/I)

- MC8/I Memory Extension Control, bank switching needed to support more than 4K words of memory

- MP8/I Memory Parity

- KE8/I Extended Arithmetic Element, which supported hardware integer multiplication and division, one-bit double-word shifts, and normalization

- KT8/I Time Sharing Hardware Modification, which allowed the computer to operate in either Executive Mode or User Mode

It could perform an addition to the accumulator in 3.0 μseconds, and a 12 by 12 bit multiplication with 24 bit result in 6.0 μseconds, using the math extension hardware.

The MC-8/I had three 3-bit registers: the Instruction Field and associated Instruction Buffer, and Data Field, which could be loaded either manually from the front panel, or under program control (by the Change Instruction Field - something of a misnomer, as it was actually the IB which was loaded - and Change Data Field instructions). The IB contents were loaded into the IF by a jump or subroutine call.

Images

External links

- PDP-8/I - Original PDP-8/I documents

| v • d • e PDP-8 Computers, Software and Peripherals |

|---|

| PDP-8s: PDP-5 • PDP-8 • LINC-8 • PDP-8/S • PDP-8/I • PDP-8/L • PDP-12 • PDP-8/E • PDP-8/F • PDP-8/M • PDP-8/A

Workstations: VT78 Also: PDP-8 family • PDP-8 architecture • PDP-8 Memory Extension units |