Difference between revisions of "MK11 memory system"

m (oops) |

m (rm dup cat) |

||

| (26 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

| − | + | [[Image:MK11Controller.jpg|thumb|250px|right|Box Controller (panel can hold up to four)]] | |

| − | It came in at least | + | The '''MK11 memory system''' was a [[Dynamic RAM|DRAM]] [[main memory]] system for the [[PDP-11/70]]. It was 32 [[bit]]s wide, to interface to the -11/70's Main Memory Bus, and provided [[Error-correcting code|ECC]] (7 bits/double-[[word]]), which could correct all single-bit errors. Read, Write, and Exchange cycles were supported. It came in at least three variants: |

| + | |||

| + | * the MK11-B (which used 32KB and 64KB [[MS11-K MOS memory]] array modules) | ||

| + | * the MK11-B-2 (which added the ability to use 256KB memory array modules). | ||

| + | * the MKA11 (a [[multi-port memory]] version for the [[PDP-11/74]]) | ||

| + | |||

| + | (It is not known if there was an MK11-A, and if so, what it was.) | ||

A maximum of eight MK11 systems could be installed on a single machine, for a maximum of slightly less than 4MB (with 64KB modules, eight MK11 systems would be needed to reach this; with 265KB modules, only two). | A maximum of eight MK11 systems could be installed on a single machine, for a maximum of slightly less than 4MB (with 64KB modules, eight MK11 systems would be needed to reach this; with 265KB modules, only two). | ||

| − | + | A separate 'Box Controller' panel module mounted in the rack controlled whether the MK11 unit was in use, what its starting [[address]] was, 'external' [[memory interleaving|interleaving]], etc. (The MK11 contains two controllers internally, and when an MK11 contains a symmetrical set of memory array modules, 'internal' interleaving between the two of them is automagically enabled.) | |

==Implementation== | ==Implementation== | ||

| − | + | [[Image:M8158MK11ABuf.jpg|thumb|250px|left|M8158 Address Buffer card (note memory bus [[terminator]]s)]] | |

| + | |||

| + | An MK11 system contained six [[DEC card form factor|hex]] control modules (of four different types), and then a group of up to eight pairs of hex memory array modules; they were all plugged into a large custom 24-slot [[backplane]] ([[DEC part number]] 70-14226-0), all housed in a [[BA11-K mounting box]]. | ||

| + | |||

| + | The control modules included a pair of memory bus interface boards (an M8158 address buffer board, and either an M8159 or M8164 data buffer board; the M8159 could only be used with 64KB memory modules, whereas the M8164 could be used with either those or 256KB modules); and two pairs of control boards (an M8160 Control A module, and an M8161 Control B module), one set for each controller of the MK11 system. The Control A modules generated timing signals, did module addressing, checked the configuration (below), and did memory refresh. The Control B modules interfaced to the memory modules, and computed and checked the ECC. | ||

| − | + | [[Image:M8159MK11DBuf.jpg|thumb|250px|right|M8159 Data Buffer card (also with memory bus terminators)]] | |

| − | The memory array modules were placed in the backplane from the inner slots (next to the buffer and control boards) toward the outer; the buffer and control boards went in the center slots. When an MK11 backplane contained a mix of different size board pairs, the smallest ones had to be in the lower locations (i.e. close to the buffer and control boards). If there were an even number of memory array boards installed, and the sizes were matched on each side, the MK11 automatically enabled [[ | + | The memory array modules were placed in the backplane from the inner slots (next to the buffer and control boards) toward the outer; the buffer and control boards went in the center slots. When an MK11 backplane contained a mix of different size board pairs, the smallest ones had to be in the lower locations (i.e. close to the buffer and control boards). If there were an even number of memory array boards installed, and the sizes were matched on each side, the MK11 automatically enabled interleaving. |

| + | |||

| + | The MKA11 added two other control boards: the M8162 Port MUX A module, and the M8163 Port MUX B module. | ||

| + | |||

| + | ===Module chart=== | ||

| + | |||

| + | The board organization in the MK11 is (viewed from the board insertion side of the backplane, not the [[wire-wrap]] pin side, as is common in [[DEC]] documentation): | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! !! colspan="6" | Connector | ||

| + | |- | ||

| + | ! Slot !! A !! B !! C !! D !! E !! F | ||

| + | |- | ||

| + | | 2 || colspan="6" style="text-align:center;" | #14 memory array | ||

| + | |- | ||

| + | | 3-8 || colspan="6" style="text-align:center;" | Arrays #2-12 | ||

| + | |- | ||

| + | | 9 || colspan="6" style="text-align:center;" | #0 memory array | ||

| + | |- | ||

| + | | 10 || colspan="6" style="text-align:center;" | M8161 control B | ||

| + | |- | ||

| + | | 11 || colspan="6" style="text-align:center;" | M8160 control A | ||

| + | |- | ||

| + | | 13 || colspan="6" style="text-align:center;" | M8158 address buffer | ||

| + | |- | ||

| + | | 15 || colspan="6" style="text-align:center;" | M8159 data buffer | ||

| + | |- | ||

| + | | 16 || colspan="6" style="text-align:center;" | M8160 control A | ||

| + | |- | ||

| + | | 17 || colspan="6" style="text-align:center;" | M8161 control B | ||

| + | |- | ||

| + | | 18 || colspan="6" style="text-align:center;" | #1 memory array | ||

| + | |- | ||

| + | | 19-24 || colspan="6" style="text-align:center;" | Arrays #3-13 | ||

| + | |- | ||

| + | | 25 || colspan="6" style="text-align:center;" | #15 memory array | ||

| + | |} | ||

| + | |||

| + | ===Cabling=== | ||

| + | |||

| + | The Box Controller panel (DEC part number 70-14274-0) was connected to the MK11 via two cables: a BC08R-10 [[flat cable]] (which plugs into [[Berg connector]] header J5 on the data buffer board), and a power control cable (DEC part number 70-14311-9F). | ||

==Upgrades== | ==Upgrades== | ||

| − | An MK11-B could be upgraded to an MK11-B-2 by swapping in an M8164 data buffer board for the M8159, and swapping in, or adding, pairs of 256KB board sets. | + | An MK11-B could be upgraded to an MK11-B-2 by swapping in an M8164 data buffer board for the M8159, and swapping in, or adding, pairs of 256KB memory array board sets. |

| + | |||

| + | [[Image:256KBMemoryArray.jpg|thumb|200px|right|M8728 256KB module]] | ||

| + | |||

| + | There were two generations of memory array modules for the MK11; the first is the MS11-K (link above; 32KB and 64KB, depending on the number of DRAM [[integrated circuit|chips]] used); the second is the M8728 (name currently unknown), which used 156 16Kx1 DRAM chips to provide a 256KB memory array module. | ||

| + | |||

| + | ===Non-standard upgrades=== | ||

| + | |||

| + | [[Image:1MBMemoryArray.jpg|thumb|200px|left|M8750 1MB module]] | ||

| + | |||

| + | A later board, the M8750, used the same [[Printed circuit board|PCB]] as the M8728, but 64Kx1 DRAM chips - the board had [[jumper]]s to allow the use of either size chip - to provide a 1MB memory array module (used in the [[VAX-11/730]] and [[VAX-11/750]]). | ||

| − | ==See also== | + | This board was not supported by the MK11. However, it is possible to use them in an MK11, with slight modifications (see the message linked below for the details). |

| + | |||

| + | Also, it is theorized that with the appropriate jumper configuration, they can be made to look like 256KB boards; this will 'waste' 3/4 of the storage on the card, but if 256KB boards are unobtainable, the fairly widely-available M8750's could be substituted. | ||

| + | |||

| + | ==CSR Access== | ||

| + | |||

| + | The control [[register]]s for the MK11 have [[address]]es in the I/O page of the PDP-11 [[UNIBUS]] [[address space]]; but the MK11 is not on the UNIBUS, so a 'trick' is needed for the [[Central Processing Unit|CPU]] to be able to gain access to them. That is to use the [[UNIBUS map]] (usually used for [[Direct Memory Access|DMA]] cycles from [[peripheral|device]]s to main memory); the [[memory management]] and UNIBUS map are set up so that CPU references to the CSRs are routed out to the UNIBUS, and then back in to the MK11. | ||

| + | |||

| + | The process for doing so from the [[front panel]] is given in the 'MK11 MOS memory technical manual', section 6.3.4, 'CSR Addressing'. That section also cryptically alludes to a "direct addressing" method (the use of the UNIBUS map, above, is referred to as an "indirect addressing" method), but it requires a "modified PDP-11/70 processor", of which no details are given (one ''hypothesis'' is that a portion of the I/O page in the CPU's address space is sent out the memory bus, not through KPAR7). | ||

| + | |||

| + | <!-- ==Further reading== -->==See also== | ||

* [[MJ11 memory system]] | * [[MJ11 memory system]] | ||

| − | + | ==External links== | |

| + | |||

| + | * [http://www.bitsavers.org/pdf/dec/pdp11/memory/EK-0MK11-TM-001_MK11mem.pdf MK11 MOS memory technical manual] (EK-0MK11-TM-001) | ||

| + | * [http://www.bitsavers.org/pdf/dec/pdp11/1170/MK11-B_Field_Maintenance_Print_Set_Oct77_part1.pdf MK11-B Field Maintenance Print Set (part 1)] | ||

| + | * [http://www.bitsavers.org/pdf/dec/pdp11/1170/MK11-B_Field_Maintenance_Print_Set_Oct77_part2.pdf MK11-B Field Maintenance Print Set (part 2)] | ||

| + | * [http://www.bitsavers.org/pdf/dec/pdp11/1170/MP00523_MK11-B_revB_Field_Maintenance_Print_Set_Mar1978.pdf MK11-B Field Maintenance Print Set] (MP00523) | ||

| + | * [https://manx-docs.org/collections/hcps/m8750.pdf M8750 Field Maintenance Print Set] (MP01398) - very faint scans | ||

| + | * [http://www.bitsavers.org/pdf/dec/vax/730/MP01270_11-730_Engineering_Drawings_198204.pdf 11/730-Z Field Maintenance Print Set (MP01270)] - the M8750 is covered in MS730-C Field Maintenance Print Set (MP01366) (pp. 292-12 of the PDF) | ||

| + | * [https://marc.info/?l=classiccmp&m=142608921824435 VAX-11/750 memory in 11/70] | ||

| + | |||

| + | [[Category: PDP-11 Memories]] | ||

Latest revision as of 01:23, 6 February 2024

The MK11 memory system was a DRAM main memory system for the PDP-11/70. It was 32 bits wide, to interface to the -11/70's Main Memory Bus, and provided ECC (7 bits/double-word), which could correct all single-bit errors. Read, Write, and Exchange cycles were supported. It came in at least three variants:

- the MK11-B (which used 32KB and 64KB MS11-K MOS memory array modules)

- the MK11-B-2 (which added the ability to use 256KB memory array modules).

- the MKA11 (a multi-port memory version for the PDP-11/74)

(It is not known if there was an MK11-A, and if so, what it was.)

A maximum of eight MK11 systems could be installed on a single machine, for a maximum of slightly less than 4MB (with 64KB modules, eight MK11 systems would be needed to reach this; with 265KB modules, only two).

A separate 'Box Controller' panel module mounted in the rack controlled whether the MK11 unit was in use, what its starting address was, 'external' interleaving, etc. (The MK11 contains two controllers internally, and when an MK11 contains a symmetrical set of memory array modules, 'internal' interleaving between the two of them is automagically enabled.)

Contents

Implementation

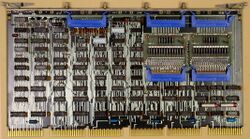

An MK11 system contained six hex control modules (of four different types), and then a group of up to eight pairs of hex memory array modules; they were all plugged into a large custom 24-slot backplane (DEC part number 70-14226-0), all housed in a BA11-K mounting box.

The control modules included a pair of memory bus interface boards (an M8158 address buffer board, and either an M8159 or M8164 data buffer board; the M8159 could only be used with 64KB memory modules, whereas the M8164 could be used with either those or 256KB modules); and two pairs of control boards (an M8160 Control A module, and an M8161 Control B module), one set for each controller of the MK11 system. The Control A modules generated timing signals, did module addressing, checked the configuration (below), and did memory refresh. The Control B modules interfaced to the memory modules, and computed and checked the ECC.

The memory array modules were placed in the backplane from the inner slots (next to the buffer and control boards) toward the outer; the buffer and control boards went in the center slots. When an MK11 backplane contained a mix of different size board pairs, the smallest ones had to be in the lower locations (i.e. close to the buffer and control boards). If there were an even number of memory array boards installed, and the sizes were matched on each side, the MK11 automatically enabled interleaving.

The MKA11 added two other control boards: the M8162 Port MUX A module, and the M8163 Port MUX B module.

Module chart

The board organization in the MK11 is (viewed from the board insertion side of the backplane, not the wire-wrap pin side, as is common in DEC documentation):

| Connector | ||||||

|---|---|---|---|---|---|---|

| Slot | A | B | C | D | E | F |

| 2 | #14 memory array | |||||

| 3-8 | Arrays #2-12 | |||||

| 9 | #0 memory array | |||||

| 10 | M8161 control B | |||||

| 11 | M8160 control A | |||||

| 13 | M8158 address buffer | |||||

| 15 | M8159 data buffer | |||||

| 16 | M8160 control A | |||||

| 17 | M8161 control B | |||||

| 18 | #1 memory array | |||||

| 19-24 | Arrays #3-13 | |||||

| 25 | #15 memory array | |||||

Cabling

The Box Controller panel (DEC part number 70-14274-0) was connected to the MK11 via two cables: a BC08R-10 flat cable (which plugs into Berg connector header J5 on the data buffer board), and a power control cable (DEC part number 70-14311-9F).

Upgrades

An MK11-B could be upgraded to an MK11-B-2 by swapping in an M8164 data buffer board for the M8159, and swapping in, or adding, pairs of 256KB memory array board sets.

There were two generations of memory array modules for the MK11; the first is the MS11-K (link above; 32KB and 64KB, depending on the number of DRAM chips used); the second is the M8728 (name currently unknown), which used 156 16Kx1 DRAM chips to provide a 256KB memory array module.

Non-standard upgrades

A later board, the M8750, used the same PCB as the M8728, but 64Kx1 DRAM chips - the board had jumpers to allow the use of either size chip - to provide a 1MB memory array module (used in the VAX-11/730 and VAX-11/750).

This board was not supported by the MK11. However, it is possible to use them in an MK11, with slight modifications (see the message linked below for the details).

Also, it is theorized that with the appropriate jumper configuration, they can be made to look like 256KB boards; this will 'waste' 3/4 of the storage on the card, but if 256KB boards are unobtainable, the fairly widely-available M8750's could be substituted.

CSR Access

The control registers for the MK11 have addresses in the I/O page of the PDP-11 UNIBUS address space; but the MK11 is not on the UNIBUS, so a 'trick' is needed for the CPU to be able to gain access to them. That is to use the UNIBUS map (usually used for DMA cycles from devices to main memory); the memory management and UNIBUS map are set up so that CPU references to the CSRs are routed out to the UNIBUS, and then back in to the MK11.

The process for doing so from the front panel is given in the 'MK11 MOS memory technical manual', section 6.3.4, 'CSR Addressing'. That section also cryptically alludes to a "direct addressing" method (the use of the UNIBUS map, above, is referred to as an "indirect addressing" method), but it requires a "modified PDP-11/70 processor", of which no details are given (one hypothesis is that a portion of the I/O page in the CPU's address space is sent out the memory bus, not through KPAR7).

See also

External links

- MK11 MOS memory technical manual (EK-0MK11-TM-001)

- MK11-B Field Maintenance Print Set (part 1)

- MK11-B Field Maintenance Print Set (part 2)

- MK11-B Field Maintenance Print Set (MP00523)

- M8750 Field Maintenance Print Set (MP01398) - very faint scans

- 11/730-Z Field Maintenance Print Set (MP01270) - the M8750 is covered in MS730-C Field Maintenance Print Set (MP01366) (pp. 292-12 of the PDF)

- VAX-11/750 memory in 11/70