Difference between revisions of "PDP-10"

(→Front ends: DC68 + DC75) |

(→Front ends: -11/40 on a KL10) |

||

| Line 56: | Line 56: | ||

The [[DL10]], connected to both an external memory bus and the I/O bus, allowed the PDP-10 CPU to control up to four [[PDP-11]]'s. The DC75 Synchronous Communication Multiplexer uses a DL10 to communicate with a [[PDP-11/20]] which has one or more DS11 Synchronous Line Interfaces to interface with 8 or more (depending on the configuration) [[synchronous serial line]]s. | The [[DL10]], connected to both an external memory bus and the I/O bus, allowed the PDP-10 CPU to control up to four [[PDP-11]]'s. The DC75 Synchronous Communication Multiplexer uses a DL10 to communicate with a [[PDP-11/20]] which has one or more DS11 Synchronous Line Interfaces to interface with 8 or more (depending on the configuration) [[synchronous serial line]]s. | ||

| − | On the KL10, up to 4 [[DTE20 Interface]]s, each of which allowed the connection of one PDP-11, could be attached. (One PDP-11, the 'master', would [[bootstrap]] the KL10, including loading the [[microcode]] | + | On the KL10, up to 4 [[DTE20 Interface]]s, each of which allowed the connection of one PDP-11, could be attached. (One PDP-11, the 'master', a [[PDP-11/40]], would [[bootstrap]] the KL10, including loading the [[microcode]]; it could also be used for other 'normal' front end activities, such as driving groups of asynchronous serial lines, providing [[DECtape]]s, etc.) |

==Software== | ==Software== | ||

Revision as of 22:11, 10 July 2021

A series of large, 36-bit word mainframe-like systems built by DEC. They were basically a re-implementation of the earlier PDP-6 architecture, whose hardware engineering had been a failure. (The machines were so similar at the programming level that PDP-6 object code could run on a PDP-10.)

DEC sold 4 different generations of PDP-10 processors: the KA10, the KI10, the KL10, and the small KS10. All except the KS10 were available in multi-processor versions with two CPUs.

PDP-10s were very important machines on the early ARPANET and Internet, being one of the few (relatively!) cheaply available machines which could run a full NCP and later TCP/IP stack as a multi-user environment at the time.

They still have a large following today, due in part to the innovative time-sharing operating systems written for them. There are several good simulators available, notably SIMH and KLH10.

Contents

Hardware

Like most mainframes, PDP-10's were composed of a number of separate free-standing units of various types (CPUs, main memory, etc), connected together with busses carried in point-point cables. Systems could be upgraded by adding additional units, or replacing existing units with enhanced successors.

Busses

DEC-10's supported a number of different busses; there are different types of bus for memory and peripherals.

There were three generations of main memory bus, and memory systems to attach to them. The first two were the so-called 'external memory bus', in KA (18-bit address) and KI (22-bit) forms (for the KA10, and KI10 and early KL10, respectively), although they also had protocol differences. The last was the 'internal memory bus', the 'S-Bus' (for the later KL10s, a later version of the S-Bus, the X-Bus, differed only in the logic family it interfaced to). The differences between the two external bus types required a KI10-M Memory Bus Adapter if KA-bit units were to be attached to a KI10. Similarly, KI-type units could be attached to the S-Bus using a DMA20 Memory Bus Controller.

For peripherals, on the KA10 and KI10 an 'I/O bus' was provided. It allowed peripherals to interrupt the CPU, and supported programmed I/O (including block transfers); speeds of up to 200K transfers/second were possible on the KA10, and 350K transfers/second on the KIl0. The DT01C I/O Bus Switch allowed an device to be switched between two different CPUs. For DMA, mass storage peripherals connected directly to memories (PDP-10 memories are generally multi-port).

On the KL10, RH20 MASSBUS controllers supported mass storage devices; a DIA20 In/Out Bus Controller could also be attached, to provide a KA10/KI10 compatible I/O bus.

The KS10, which was sui generis, had its own custom memory bus, which appeared only on the main backplane. For I/O, it used the UNIBUS and (via RH11's) the MASSBUS.

On the KA10, all the busses were physically instantiated as cables with a pair of dual width PCBs at each end, which plugged into slots in a standard DEC backplane; these later became the CJ connectors. On the KI10 and KL10s with an external memory bus, the memory bus cables ended in a large QuickLatch connector; these connectors were also used on the CPU end of I/O bus cables of that machine.

Devices

In the KA10 and KI10, high-speed mass storage device controllers generally connected to both i) a channel, the DF10 Data Channel, which attached to an external memory bus, and ii) the I/O bus. The CPU controlled the channel via the device controller. This setup was used to connect mass storage controllers, such as:

- RP10 disk controller - RP01, RP02 and RP03 disk drives

- RC10 disk/drum system - RD10 fixed-head disk, RM10B drum

- TM10 Magnetic Tape Control - TU10 and others

The RH10 MASSBUS controller (which appeared toward the end of the KI10 period), for MASSBUS mass storage devices, was similarly connected (to a DF10 channel, and the I/O bus).

Other optional devices (the paper tape reader and punch, and console asynchronous serial line, were standard), which connected to the I/O bus, included:

- TD10 DECtape Control- TU55

- BA10 Hardcopy Control - LP10 line printer, XY10 plotter, CR10 card reader, CP10 card punch

- DC10 asynchronous serial line controller

- DS10 synchronous serial line controller

On the KL10, up to 8 RH20 MASSBUS controllers could be connected to the system.

Front ends

PDP-10's made use of front end computers from an early stage.

The DA10 Twelve- and Eighteen-Bit Computer Interface, which connected to the I/O bus, allowed a computer such as a PDP-8/I to exchange data with a PDP-10. The DC68A Data Communication System uses a DA10 to communicate with a PDP-8/I which has a DC08 Serial Line Multiplexer to interface with up to 128 asynchronous serial lines.

The DL10, connected to both an external memory bus and the I/O bus, allowed the PDP-10 CPU to control up to four PDP-11's. The DC75 Synchronous Communication Multiplexer uses a DL10 to communicate with a PDP-11/20 which has one or more DS11 Synchronous Line Interfaces to interface with 8 or more (depending on the configuration) synchronous serial lines.

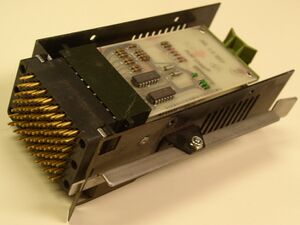

On the KL10, up to 4 DTE20 Interfaces, each of which allowed the connection of one PDP-11, could be attached. (One PDP-11, the 'master', a PDP-11/40, would bootstrap the KL10, including loading the microcode; it could also be used for other 'normal' front end activities, such as driving groups of asynchronous serial lines, providing DECtapes, etc.)

Software

The first three generations of PDP-10's were marketed as the DECsystem-10, running the TOPS-10 operating system; the third was also sold as the DECSYSTEM-20, running TOPS-20. (The varying capitalization was the result of a trademark infringment suit.)

Two other very important operating systems also ran on PDP-10's: MIT's ITS (a very advanced system, from whence came EMACS, and much more besides), and TENEX, which DEC later turned into TOPS-20.

Others

The 36-bit line was cancelled by DEC many times. The PDP-6 was difficult to manufacture and maintain, and only 23 were sold; it was cancelled not long after its introduction. However, it made a comeback as the PDP-10, which was a success. Its uncertain future allowed a number of small vendors to sell PDP-10 'clones'.

Cancelled DEC projects

- KXF10 "Dolphin", cancelled around 1978.

- KT20 "Minnow", cancelled around 1979.

- KC10 "Jupiter", cancelled 1983.

- KD10

Clones

Two PDP-10 clones were built at Xerox PARC, since that was easier than trying to convince Xerox top management to allow the purchase of a relatively expensive machine from a direct competitor.

Commercial

- Foonly: F-1, F2, F3, F4, F5 (unfinished)

- Systems Concepts: SC-30M, SC-40

- Tymshare: System 26, System 26KL.

- CompuServe: JRG-1 (unfinished)

- XKL: TOAD-1, TOAD-2

Hobbyist recreations

- David Conroy: PDP-10/X

- Neil Franklin: (unfinished)

- Rob Doyle: KS10 FPGA

- David Bridgham: KV10 (in progress)

- Angelo Papenhoff: FPDPGA, PDP-6 and KA10 FPGA.

Software simulators

- S W Galley: virtual machine PDP-10

- Megan Gentry: sim10

- Stu Grossman: kx10

- Ken Harrenstien: KLH10

- Eric Smith: (unfinished)

- Daniel Seagraves: e10

- Tim Stark: ts10, MSE

- Bob Supnik: KS10 simulator for SIMH.

- Richard Cornwell: PDP-6, KA10, KI10, and KL10 simulators for SIMH

- Angelo Papenhoff: PDP-6 simulator

- Bruce Baumgart: WAITS reenactment

- Jeff Parsons: PCjs

- Mark Garrett: TITAN

See also

Further reading

- PDP-10 Interface Manual (DEC-10-HIFB-D) - Covers all the busses

External links

- Bitsavers PDP-10 documents

- DECsystem-10 Technical Summary

- EK-108OU-PD-002, "KL10-Based Physical Description" - Has images of CJ dual card connectors and QuickLatch connectors, pp. 69-70

- nocrew's PDP-10 stuff

- PDP-10 Models

- PDP-10 I/O Structure

- The DEC PDP-10 Emulation Webpage