Difference between revisions of "ITS machine configurations"

m (→AI KA10: link Fabritek Core Memory) |

(→KS10's: Add image of AI+ML/MC) |

||

| Line 96: | Line 96: | ||

* 'KL-UDGE' LH 1822 interface (maybe a clock, too) | * 'KL-UDGE' LH 1822 interface (maybe a clock, too) | ||

| − | == | + | ==KS10's== |

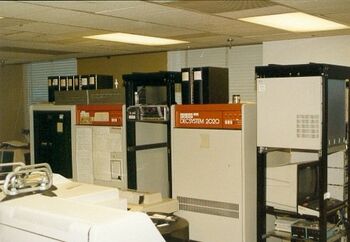

| − | The [[KS10]]'s were all pretty stock, hardware-wise; like the KL10, they also ran custom microcode. | + | [[File:AI+MC_KS10s.jpg|350px|thumb|right|The AI (left) and MC (probably; perhaps ML) KS10s]] |

| + | |||

| + | The [[KS10]]'s were all pretty stock, hardware-wise; like the KL10, they also ran custom microcode. | ||

| + | |||

| + | ===AI KS10=== | ||

* Disk [[RH11 MASSBUS controller]] | * Disk [[RH11 MASSBUS controller]] | ||

Revision as of 01:13, 17 November 2024

The configuration of the various Incompatible Timesharing System time-sharing PDP-10 mainframes at MIT (in the AI Lab, where it was born, and in LCS, only other organization to run it 'in production') are given here. They were all physically in Technology Square.

Contents

AI PDP-6

- The first PDP-6 at MIT. At first, in only had 16KW of core memory. A 256KW Fabritek Core Memory was delivered summer 1966, but not fully working until a year later. When time-sharing moved to the newer PDP-10, the PDP-6 was reduced to the 16KW memory again.

- One console teletype.

- In summer 1966, the teletype logic was modified by Tom Knight to support four more teletypes.

- GE Datanet 760 with four CRT consoles.

- MAR and one-proceed to support debugging under time-sharing.

- Briefly, Analex disk drive.

- Data Disc M-6 disk drives.

- IBM 2311 disk interface.

DM PDP-6

- 32K core memory.

AI KA10

The AI machine was the first KA10 at MIT. It was initially installed as a 'slave' processor to the AI PDP-6 in a tightly-coupled multi-processor; later the two machines swapped roles. It was the first KA10 there to support virtual memory (an MIT custom modification).

- Eventually, 512KW of core memory: the 256KW Fabritek Core Memory moby, and another 256KW Ampex ARM10. Later they both (I think) went away, and HIC added a memory box that used CADR memory boards.

- Systems Concepts DC-10 - disk controller

- 8 x Calcomp 215 drives

- TM10A

- Rubin 10-11 interface

- DH 1822 interface

- Systems Concepts DK-10

- TK10 TTY scanner

The 'Arpanet Resources Handbook' gives the speed of the two mobies as 2.8 μseconds and 1.1 μseconds; the former seems to be the Fabritek, so the other must be the Ampex.

DM KA10

Another KA10, with a Systems Concepts DM-10 paging box, and also:

- 2 x 128KW MD10's

- a collection of other DEC early memory boxes (MA10's and/or MB10's) totalling 256KW

- RP10

- Its DF10

- TM10B

- Its DF10 (or did it share the other one?)

- Metcalfe DH 1822 interface

- Morton serial line box

ML KA10

Another KA10 with a DM-10, and also:

- 4 x 128KW MD10's

- RP10

- 4 x RP03's

- 4 x Calcomp 215's

- Its DF10

- TM10A

- TU20

- DH 1822 interface

- eventually, a CH10

MC KL10

The CPU was a stock Model A; it ran custom microcode, though, to implement the 'MIT paging box'. The main memory and channels were also 100% stock. Also:

- 8 x MF10's (originally); later upgraded to MH10's.

- (later) An Ampex ARM10L 'external' memory box

- An RH10

- 3 RP04's

- Its DF10

- TM10B

- Its DF10

- A DTE20

- A DL10

- Another PDP-11/40, the 'IO-11'

- DH11

- Gould 5200 - later moved over to Plasma

- Later, a Trident controller

- Initially one, eventually three Trident T-300 drives

- Eventually two CH11's

- Another PDP-11/40, the 'IO-11'

- 'KL-UDGE' LH 1822 interface (maybe a clock, too)

KS10's

The KS10's were all pretty stock, hardware-wise; like the KL10, they also ran custom microcode.

AI KS10

- Disk RH11 MASSBUS controller

- 2 x RP06

- Tape RH11

- LH-DH/11 Local/Distant Host Controller

- CH11

- DZ11

MC KS10

No tape drive; backups must have been done over the Chaosnet.

- Disk RH11

- RP06

- LH-DH/11

- CH11

- DZ11

ML KS10

- Disk RH11

- RP06

- CH11

- 4 x DZ11

MD KS10

- Disk RH11

- CH11

- 4 x DZ11

See also

External links

- SYSTEM - archive of CONFIG > files

- Philippe Brou's images

- ML PDP-10 - back row, from the right: CPU, pager, 4xMD10 memories, RP10? and its DF10?

- Knight TV Controller - at short wall end

- MC KL-10 - several images

- One wing - MF10's; also RH10 and its DF10 at the far end

- Memories - ARM10 on right, with MF10's behind

- The other wing - from right, the TM10, its DF10, the DL10, the 'I/O-11' (in blank cabinet), and the first Trident

- Hardware info from David Moon

- The Magic Switch