Difference between revisions of "PDP-11/44"

(give CPU) |

(→External links: +FMPS, manuals; list EUB memories it can use) |

||

| Line 9: | Line 9: | ||

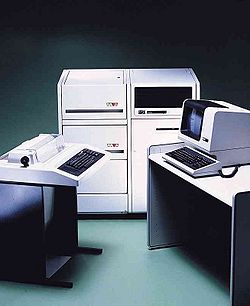

[[Image:PDP11-44-geerol.jpg|150px|thumb|right|A PDP-11/44 setup]] | [[Image:PDP11-44-geerol.jpg|150px|thumb|right|A PDP-11/44 setup]] | ||

| − | The '''PDP-11/44''' was a high performance [[UNIBUS]] [[PDP-11]] system; in some senses a lower-cost successor to the [[PDP-11/70]], although without the very high [[main memory]] bandwidth and I/O bandwidth to [[mass storage]] of the -11/70, as it lacked the latter's Main Memory Bus and integrated [[MASSBUS]], relying instead on the UNIBUS. Its [[Central Processing Unit|CPU]], the [[KD11-Z CPU|KD11-Z]], was the last PDP-11 CPU to be made out of discrete [[integrated circuit|chips]], and not a [[microprocessor]]. | + | The '''PDP-11/44''' was a high performance [[UNIBUS]] [[PDP-11]] system; in some senses a lower-cost successor to the [[PDP-11/70]], although without the very high [[main memory]] bandwidth and I/O bandwidth to [[mass storage]] of the -11/70, as it lacked the latter's Main Memory Bus and integrated [[MASSBUS]], relying instead on the UNIBUS, and [[Extended UNIBUS|EUB]]. Its [[Central Processing Unit|CPU]], the [[KD11-Z CPU|KD11-Z]], was the last PDP-11 CPU to be made out of discrete [[integrated circuit|chips]], and not a [[microprocessor]]. |

| − | The -11/44 used the | + | The -11/44 used the EUB for its [[bus]] to main memory, allowing it to have up to 4 mega-[[byte]]s of main memory. All devices were attached to a semi-separate UNIBUS (it and the EUB shared data lines, but not [[address]] lines); [[Direct Memory Access|DMA]] devices could gain access to the memory via a [[UNIBUS map]] which connected the two, and mapped UNIBUS addresses to main memory addresses. |

| − | Full [[PDP-11 Memory Management]] and a [[cache]] (the [[KK11- | + | Full [[PDP-11 Memory Management]] and a [[cache]] (the [[KK11-B Cache Memory|KK11-B]]) were standard on all -11/44's. It also supported the optional [[FP11-F Floating-Point Processor|FP11-F]] [[floating point]] (full [[FP11 floating point]]), and/or the [[KE44-A Commercial Instruction Set Processor]] (the [[PDP-11 Commercial Instruction Set]]). |

| + | |||

| + | The -11/44 initially shipped with [[MS11-M MOS memory|MS11-M]]; the [[MS11-P MOS memory|MS11-P]] became available later, and was also useable in the -11/44. | ||

Its main [[mounting box]] was the new [[BA11-A mounting box]]. | Its main [[mounting box]] was the new [[BA11-A mounting box]]. | ||

| Line 30: | Line 32: | ||

1979. A middle-class -11. It had the 22-bit UNIBUS map and MMU as standard (up to 2 Mwords on a separate CPU-memory interconnect, called the PAX Memory Bus). The CPU consists of 5 boards, plus one for the FPP (FP11-F, optional), and two CIS (KE44-A, optional). Features: 8 KByte cache, ODT, 2 SLU's (Serial Line Units: console + TU58 console media), RTC (Real-Time Clock), kernel/supervisor/user modes. | 1979. A middle-class -11. It had the 22-bit UNIBUS map and MMU as standard (up to 2 Mwords on a separate CPU-memory interconnect, called the PAX Memory Bus). The CPU consists of 5 boards, plus one for the FPP (FP11-F, optional), and two CIS (KE44-A, optional). Features: 8 KByte cache, ODT, 2 SLU's (Serial Line Units: console + TU58 console media), RTC (Real-Time Clock), kernel/supervisor/user modes. | ||

| − | The machine also had an almost-FEP (front-end processor) console, based on the Intel i8088, running from PROM. There was no | + | The machine also had an almost-FEP (front-end processor) console, based on the Intel i8088, running from PROM. There was no QBUS equivalent. |

Trivia: This was the last non-[[microprocessor]]-based PDP-11.</i> | Trivia: This was the last non-[[microprocessor]]-based PDP-11.</i> | ||

| − | {{PDP-11}} | + | ==External links== |

| + | |||

| + | * [http://bitsavers.org/pdf/dec/pdp11/1144/ PDP-11/44] - Bitsavers | ||

| + | ** [http://bitsavers.org/pdf/dec/pdp11/1144/1144_UsersGuide.pdf PDP-11/44 System User's Guide] (EK-11044-UG-003) | ||

| + | ** [http://bitsavers.org/pdf/dec/pdp11/1144/1144_SystemTechMan.pdf PDP-11/44 System Technical Manual] (EK-KD11Z-TM-001) | ||

| + | ** [http://bitsavers.org/pdf/dec/pdp11/1144/MP00897_11X44sys_Dec79.pdf 11X44 Field Maintenance Print Set] (MP00897) | ||

| + | |||

| + | {{Nav PDP-11}} | ||

[[Category:UNIBUS PDP-11s]] | [[Category:UNIBUS PDP-11s]] | ||

Revision as of 16:10, 16 January 2022

| PDP-11/44 | |

PDP-11/44 from a sales brochure. | |

| Manufacturer: | Digital Equipment Corporation |

|---|---|

| Architecture: | PDP-11 |

The PDP-11/44 was a high performance UNIBUS PDP-11 system; in some senses a lower-cost successor to the PDP-11/70, although without the very high main memory bandwidth and I/O bandwidth to mass storage of the -11/70, as it lacked the latter's Main Memory Bus and integrated MASSBUS, relying instead on the UNIBUS, and EUB. Its CPU, the KD11-Z, was the last PDP-11 CPU to be made out of discrete chips, and not a microprocessor.

The -11/44 used the EUB for its bus to main memory, allowing it to have up to 4 mega-bytes of main memory. All devices were attached to a semi-separate UNIBUS (it and the EUB shared data lines, but not address lines); DMA devices could gain access to the memory via a UNIBUS map which connected the two, and mapped UNIBUS addresses to main memory addresses.

Full PDP-11 Memory Management and a cache (the KK11-B) were standard on all -11/44's. It also supported the optional FP11-F floating point (full FP11 floating point), and/or the KE44-A Commercial Instruction Set Processor (the PDP-11 Commercial Instruction Set).

The -11/44 initially shipped with MS11-M; the MS11-P became available later, and was also useable in the -11/44.

Its main mounting box was the new BA11-A mounting box.

xs4all.nl

Quoting http://www.xs4all.nl/~geerol/en/GAL/index.html (1979) The PDP 11/44 (hostname "gigant") is a low-cost successor of the PDP 11/70. The 11/70, brought to the market in 1975, was the first "large" PDP. Large means a 22 bit address space and a memory limit of 4MB. Do keep in mind that user programs are still limited to 16 bit addressing and hence restricted to a limit of just 2x 64KB, when using separated I&D.

The cost of a new 11/44 has been about half of the listprice of an 11/70. The PDP 11/44 had no Massbus like the /70 has, so it was not possible to use diskdrives with a transfer rate too high.

hampage.hu

Quoting: 1979. A middle-class -11. It had the 22-bit UNIBUS map and MMU as standard (up to 2 Mwords on a separate CPU-memory interconnect, called the PAX Memory Bus). The CPU consists of 5 boards, plus one for the FPP (FP11-F, optional), and two CIS (KE44-A, optional). Features: 8 KByte cache, ODT, 2 SLU's (Serial Line Units: console + TU58 console media), RTC (Real-Time Clock), kernel/supervisor/user modes.

The machine also had an almost-FEP (front-end processor) console, based on the Intel i8088, running from PROM. There was no QBUS equivalent.

Trivia: This was the last non-microprocessor-based PDP-11.

External links

- PDP-11/44 - Bitsavers

- PDP-11/44 System User's Guide (EK-11044-UG-003)

- PDP-11/44 System Technical Manual (EK-KD11Z-TM-001)

- 11X44 Field Maintenance Print Set (MP00897)

| v • d • e PDP-11 Computers and Peripherals |

|---|

| UNIBUS PDP-11s - PDP-11/20 • PDP-11/15 • PDP-11/35 • PDP-11/40 • PDP-11/45 • PDP-11/50 • PDP-11/55 • PDP-11/70 PDP-11/05 • PDP-11/10 • PDP-11/04 • PDP-11/34 • PDP-11/60 • PDP-11/44 • PDP-11/24 • PDP-11/84 • PDP-11/94 QBUS PDP-11s - PDP-11/03 • PDP-11/23 • PDP-11/23+ • MicroPDP-11/73 • MicroPDP-11/53 • MicroPDP-11/83 • MicroPDP-11/93 QBUS CPUs: LSI-11 • LSI-11/2 • KDF11-A • KDF11-B • KDJ11-A • KDJ11-B • KDJ11-D • KDJ11-E Buses: UNIBUS • UNIBUS map • SPC • MUD • EUB • QBUS • CD interconnect • PMI Also: PDP-11 architecture • PDP-11 Extended Instruction Set • FP11 floating point • PDP-11 Memory Management |

| UNIBUS CPUs: KA11 • KC11 • KB11-A • KB11-B • KB11-C • KB11-D • KD11-A • KD11-B • KD11-D • KD11-E • KD11-EA • KD11-K • KD11-Z • KDF11-U

Co-processors: FP11-A • FP11-B • FP11-C • FP11-E • FP11-F • KE44-A • FPF11 Chips: LSI-11 • KEV11-A • KEV11-B • KEV11-C • F-11 • KEF11-A • KTF11-A • T-11 • J-11 • FPJ11 CPU options: KE11-E • KE11-F • KJ11-A • KT11-C • KT11-D • KK11-A • KK11-B • KT24 • KTJ11-B Rare CPU options: KS11 Memory Protection and Relocation option • KT11-B Paging Option • KUV11 Writeable Control Store Front panels: KY11-A • KY11-D • KY11-J • KY11-LA • KY11-LB • KY11-P More on buses: UNIBUS and QBUS termination • Bus Arbitration on the Unibus and QBUS • CTI BUS PDT-11s - PDT-11/110 • PDT-11/130 • PDT-11/150 CTI PDP-11s - PRO-325 • PRO-350 • PRO-380 Other: FIS floating point • PDP-11 Commercial Instruction Set • PDP-11 stacks • PDP-11 family differences |