KT11-B Technical Manual

As a Special Systems Option, the KT11-B does not have the usual DEC Technical Manual. This page attempts to provide at least the high-level portions of such a manual.

Note:: The KT11-B theory of operation (either from the page above, or the Option Description manual), must be thoroughly understood before trying to read this page. In particular, register names must be known, as well as the function of high-level internal entities such as the associative memory and the scratchpad memory.

Contents

Prints

The Engineering Drawings for the KT11-B (7605071) include the following logic prints:

| Number | Page Count | Content |

|---|---|---|

| 2 | 2 | Address Bus and Control Logic |

| 3 | 1 | State Control Logic |

| 4 | 1 | SP Input Mux |

| 5 | 2 | Associative Memory Control |

| 6 | 1 | Scratch Pad and State Control Logic |

| 7 | 3 | Data Bus and Control Logic |

| 8 | 1 | Keys and Associative Memory |

| 9 | 1 | XP Option for KT11 Associative Memory Control |

| 10 | 1 | PGM Register |

| 11 | 1 | PGC Register |

| 12 | 1 | Timing Logic |

| 13 | 1 | Buffered Signals and Main Logic |

| 14 | 1 | Extended Associative Memory |

| 15 | 1 | KA11 to KT11 Interface |

| 17 | 1 | KT11-B Bus Connectors |

The KT11-B is not composed of discrete boards, but rather a large number of mostly small Flip Chips plugged into a custom-wired backplane, so the division into drawings, some of which are multi-sheet (as opposed to them all being single-sheet) is a bit arbitrary. It is probably intended to align the drawings with the high-level internal structure.

Drawing Conventions

The drawings are somewhat easier to understand if the conventions used in the drawings are understood. Although no document lists them, they can be ascertained by study of the drawings.

Signal Names

Signal names in this drawing set usually start with 'Dxx', where 'xx' is related to the drawing number (given in the table above). (This is similar to the convention in the KA11 drawings, where 'Kxx-y' means that the signal originates on page y of drawing xx.) Note that the 'Dxx' correspondence seems to sometimes be off by one; i.e. a signal tagged 'D04' can be found originating on drawing 05.

In signal names of the form 'XXX (yy)', 'yy' is a bit number (in standard PDP-11 order) in a register or bus. For signals which are provided in both asserted low and asserted high forms, one will see signal names of the form 'XXX (y)', where 'y' is 1 or 0. Note that sometimes these two notations are combined, and one can find signal names of the form 'XXX (yy) (z)'. Inverted (asserted low) signals are also sometimes shown as '-XXX'.

The following specific signal names have the meaning given:

- Signals of the form 'x.y' are states, with 'x' being the major state, and 'y' being the minor state.

- Signal names starting with 'SP' refer to the scratchpad memory, which holds both cache page table entries, as well as some KT11-B registers; SPIN is its input bus, and SPDA is its output bus.

- Signal names starting with 'AM' refer to the associative memory.

- Signal names starting with 'DV' refer to the UNIBUS from the KT11-B to the devices and memory of the system.

- Signal names starting with 'CP' refer to the UNIBUS to the KT11-B from the KA11 CPU.

- Signal names starting with 'PGC' refer to the contents of the Control Status register.

- Signal names starting with 'PGM' refer to the contents of the Maintainence register.

Common Circuits

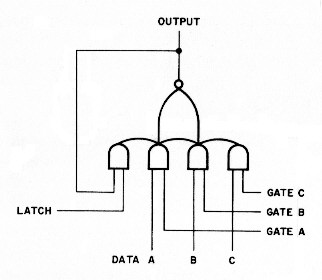

This circuit (first used in the KA11) is seen in several places in the KT11-B. It is almost always seen as an array of identical circuits, since it provides a 3-input multiplexor with latching capability, and it is used on data paths (usually 16 bits wide).

The latch is cleared by de-asserting the 'Latch' input; data from any of the three inputs (A, B, C) may then be selected for output, and potentially storage, by asserting the matching 'Gate' input. Asserting 'Latch' then stores the current output of the mux.

(Asserting more than one input simultaneously ORs the two inputs together; this capability is used in the KA11, but probably not here.)

States

The KT11-B has a state composed of two parts, the 'X' or major part, and the 'Y' or minor part; the progression of this through the various states is the major control mechanism in the KT11-B.

The X state counter is on print 12; it is composed of a 2-bit counter (allegedly a shift register, but that could not generate 4 discrete states) composed of a pair of D flops, with 4 AND gates with inverting inputs to create individual major state outputs, signals 'XSRx' (x = 0-3).

The Y state counter is an M826 Flip Chip, shown on print 8; its outputs are signals 'YSRx' (x = 0, 1 ,3, 7, 15, 14, 12, 8). (The odd sequence of minor state numbers, and the fact that they are not in numerical order, is confusing, but since that's what's on the prints, that nomenclature has to be used.)

The two groups of signals are combined into signals which indicate that the KT11-B is in that state, for each individual major/minor state, by NAND gates shown on drawing 12; inverters then provide non-inverted forms of each.

There are 4 signals XSHL, XSHR, YSHL, YSHR which control state transitions.

State Table

The following table shows the state transitions:

| State | Next State(s) | Comment |

|---|---|---|

| 0.0 | 0.8, 1.0 | Idle |

| 0.8 | 0.12 | Interrupt, Trap and Start User |

| 0.12 | 0.14 | |

| 0.14 | 0.15 | |

| 0.15 | 0.7A | |

| 0.7A | 0.3A | |

| 0.3A | 0.1A | |

| 0.1A | 0.0 | |

| 0.7B | 0.3B | Although the state names are identical to the preceding ones, this is shown on the state diagram as a separate state loop |

| 0.3B | 0.1B | Window? |

| 0.1B | 1.1 | |

| 1.0 | 1.1, 3.0 | |

| 1.1 | 1.3 | |

| 1.3 | 1.7, 3.3 | Exec-per-Process |

| 1.7 | 0.7B, 1.15 | |

| 1.15 | 1.14 | Page Violation? |

| 1.14 | 1.12 | |

| 1.12 | 0.12 | |

| 1.8 | 1.0 | |

| 2.0 | 0.0 | |

| 2.1 | 2.0, 2.3 | Shared Entry? |

| 2.3 | 2.7 | |

| 2.7 | 2.15 | |

| 2.15 | 2.14 | Page Violation? |

| 2.14 | 0.14 | |

| 2.12 | - | State does not exist |

| 2.8 | - | State does not exist |

| 3.0 | 2.0, 3.1, 3.8 | |

| 3.1 | 1.1, 2.1, 3.0 | |

| 3.3 | 3.1, 3.7A | |

| 3.7A | 1.7 | Although the state name is identical to the preceding ones, this is shown on the state diagram as a separate state loop |

| 3.7B | 3.3 | |

| 3.15 | 3.7B | |

| 3.14 | 3.15 | |

| 3.12 | 3.14 | |

| 3.8 | 1.8, 3.12 |

This table is a transcription of the single-page one in the KT11-B Option Description; that diagram contains a number of labels, but it is not completely clear which states (or transitions) the labels apply to. Over time the hope is to check this table against the multi-page table in that document, and also better described what each state means.

Construction

As mentioned, the KT11-B is constructed out of a large number of smaller Flip Chips. The card type usage counts are:

| Type | Function | Count | Comment |

|---|---|---|---|

| M111 | 16 x Inverters | 10 | 9? |

| M112 | 10 x 2-input NOR | 5 | 4? (but there's a '117' could be 112) |

| M116 | 6 x 4-input NOR | 10 | |

| M133 | 10 x 2-input NAND | 24 | |

| M135 | 8 x 3-input NAND | 6 | |

| M139 | 3 x 8-input NAND | 1 | |

| M167 | Magnitude comparator | 1 | |

| M203 | 8 x R/S flip flops | 1 | |

| M206 | 6 x D flip flops | 1 | |

| M207 | 6 x J/K flip flops | 1 | |

| M225 | Scratchpad memory | 1 | 2 for 24 cache entries |

| M240 | R/S flip flop | 1 | |

| M244 | Mutiplexor latch | 6 | |

| M259 | Associative memory | 4 | 12 for 24 cache entries |

| M602 | 2 x Pulse amplifier | 1 | |

| M611 | 14 x Power inverter | 3 | |

| M627 | 6 x NAND amplifier | 7 | |

| M721 | UNIBUS transceiver | 4 | |

| M783 | 12 x UNIBUS NAND transmitters | 6 | |

| M784 | 16 x UNIBUS inverter receivers | 2 | |

| M826 | Clock/shift register | 1 |

(The counts are from the list in the "KT11-B Option Description" document; they have been cross-checked against the 'Module Utilization' sheet from the KT11-B Engineering Drawings, and there are still some variances to be sorted out.)

| v • d • e PDP-11 Computers and Peripherals |

|---|

| UNIBUS PDP-11s - PDP-11/20 • PDP-11/15 • PDP-11/35 • PDP-11/40 • PDP-11/45 • PDP-11/50 • PDP-11/55 • PDP-11/70 PDP-11/05 • PDP-11/10 • PDP-11/04 • PDP-11/34 • PDP-11/60 • PDP-11/44 • PDP-11/24 • PDP-11/84 • PDP-11/94 QBUS PDP-11s - PDP-11/03 • PDP-11/23 • PDP-11/23+ • MicroPDP-11/73 • MicroPDP-11/53 • MicroPDP-11/83 • MicroPDP-11/93 QBUS CPUs: LSI-11 • LSI-11/2 • KDF11-A • KDF11-B • KDJ11-A • KDJ11-B • KDJ11-D • KDJ11-E Buses: UNIBUS • UNIBUS map • SPC • MUD • EUB • QBUS • CD interconnect • PMI Also: PDP-11 architecture • PDP-11 Extended Instruction Set • FP11 floating point • PDP-11 Memory Management |

| UNIBUS CPUs: KA11 • KC11 • KB11-A • KB11-B • KB11-C • KB11-D • KD11-A • KD11-B • KD11-D • KD11-E • KD11-EA • KD11-K • KD11-Z • KDF11-U

Co-processors: FP11-A • FP11-B • FP11-C • FP11-E • FP11-F • KE44-A • FPF11 Chips: LSI-11 • KEV11-A • KEV11-B • KEV11-C • F-11 • KEF11-A • KTF11-A • T-11 • J-11 • FPJ11 CPU options: KE11-E • KE11-F • KJ11-A • KT11-C • KT11-D • KK11-A • KK11-B • KT24 • KTJ11-B Rare CPU options: KS11 Memory Protection and Relocation option • KT11-B Paging Option • KUV11 Writeable Control Store Front panels: KY11-A • KY11-D • KY11-J • KY11-LA • KY11-LB • KY11-P More on buses: UNIBUS and QBUS termination • Bus Arbitration on the Unibus and QBUS • CTI BUS PDT-11s - PDT-11/110 • PDT-11/130 • PDT-11/150 CTI PDP-11s - PRO-325 • PRO-350 • PRO-380 Other: FIS floating point • PDP-11 Commercial Instruction Set • PDP-11 stacks • PDP-11 family differences |