Difference between revisions of "MS11 Semiconductor Memory System"

(Add pic) |

(Parity registers) |

||

| Line 8: | Line 8: | ||

In all versions, each bank included a controller board, and up to 4 storage boards; all cards were [[DEC card form factor|hex]] size. Each bank had to be all MOS or all bipolar (one size); however, there could be one bipolar bank and one MOS bank. | In all versions, each bank included a controller board, and up to 4 storage boards; all cards were [[DEC card form factor|hex]] size. Each bank had to be all MOS or all bipolar (one size); however, there could be one bipolar bank and one MOS bank. | ||

| + | |||

| + | ==Parity== | ||

The storage boards were available in both non-[[parity]] and parity versions (except the larger bipolar ones, which were available in parity only), the latter being indicated by a trailing '-YA' on the board number. | The storage boards were available in both non-[[parity]] and parity versions (except the larger bipolar ones, which were available in parity only), the latter being indicated by a trailing '-YA' on the board number. | ||

| + | |||

| + | Information on the parity control [[register]]s can be found in the ''pdp-11/45 processsor handbook'' (1972 and 1973 editions) where a little-known "Appendix E: Memory Parity", referred to in "2.5.6 Memory Parity", indicates that there are "16 memory status registers ... each one associated with an 8K section of memory". | ||

| + | |||

| + | These sound from the writeup like they are in the KB11-A CPU, but in fact they are in the MS11 controller board. | ||

| + | |||

| + | They can control, for each 4k block of that section, whether the memory uses odd or even parity, whether parity is enabled for that section, and whether a parity error will cause the machine to [[halt]] or [[trap]]. | ||

==MS11-B MOS== | ==MS11-B MOS== | ||

Revision as of 16:07, 5 February 2019

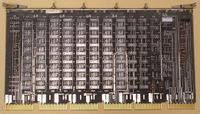

The MS11 Semiconductor Memory Systems were a set of special high-speed memories for the PDP-11/45, which plugged into special dedicated, pre-wired slots in the backplane of the the KB11-A and KB11-D CPU.

The MS11 was dual-ported memory, with one port connected to the separate 'B' UNIBUS of the PDP-11/45, and the other to the CPU through a special bus, the Fastbus. A PDP-11/45 could have up to two separate MS11 banks.

There were three different versions: initially the MS11-B MOS (450 nsec) and MS11-C bipolar memory (300 nsec); and later the MS11-A larger, but otherwise identical, bipolar memory.

Any version could be added to a stock PDP-11/45, but DEC sold versions of that machine pre-configured with MOS or bipolar as the PDP-11/50 and PDP-11/55, respectively.

In all versions, each bank included a controller board, and up to 4 storage boards; all cards were hex size. Each bank had to be all MOS or all bipolar (one size); however, there could be one bipolar bank and one MOS bank.

Parity

The storage boards were available in both non-parity and parity versions (except the larger bipolar ones, which were available in parity only), the latter being indicated by a trailing '-YA' on the board number.

Information on the parity control registers can be found in the pdp-11/45 processsor handbook (1972 and 1973 editions) where a little-known "Appendix E: Memory Parity", referred to in "2.5.6 Memory Parity", indicates that there are "16 memory status registers ... each one associated with an 8K section of memory".

These sound from the writeup like they are in the KB11-A CPU, but in fact they are in the MS11 controller board.

They can control, for each 4k block of that section, whether the memory uses odd or even parity, whether parity is enabled for that section, and whether a parity error will cause the machine to halt or trap.

MS11-B MOS

The MS11-B consisted of:

- MS11-BC or -BD MOS Memory Control (M8110)

- MS11-BM, -BP, -BR and -BT 4K MOS Memory Matrix (G401)

In addition, the MS11-B required the special H746 MOS Regulator power supply module, which produced the special voltages needed by this memory.

The -BC and -BD variants are DEC nomenclature for the first and second controllers, both being packaged with an H746, but only the former also included the needed extra H744. The -BM and -BP are the nomenclature for the non-parity and parity versions.

MS11-C Bipolar

The MS11-C consisted of:

- MS11-CC Bipolar Memory Control (M8110)

- MS11-CM, -CP 1K Bipolar Memory Matrix (M8111)

The M8110 was later replaced by the M8120, which used the same printed circuit board, but with (as yet un-determined) component variations. The -CM and -CP are the nomenclature for the non-parity and parity versions.

MS11-A Bipolar

The MS11-A consisted of:

- MS11-CC Bipolar Memory Control (M8120)

- MS11-AP 4K Bipolar Memory Matrix (M8121)

| v • d • e PDP-11 Computers and Peripherals |

|---|

| UNIBUS PDP-11s - PDP-11/20 • PDP-11/15 • PDP-11/35 • PDP-11/40 • PDP-11/45 • PDP-11/50 • PDP-11/55 • PDP-11/70 PDP-11/05 • PDP-11/10 • PDP-11/04 • PDP-11/34 • PDP-11/60 • PDP-11/44 • PDP-11/24 • PDP-11/84 • PDP-11/94 QBUS PDP-11s - PDP-11/03 • PDP-11/23 • PDP-11/23+ • MicroPDP-11/73 • MicroPDP-11/53 • MicroPDP-11/83 • MicroPDP-11/93 QBUS CPUs: LSI-11 • LSI-11/2 • KDF11-A • KDF11-B • KDJ11-A • KDJ11-B • KDJ11-D • KDJ11-E Buses: UNIBUS • UNIBUS map • SPC • MUD • EUB • QBUS • CD interconnect • PMI Also: PDP-11 architecture • PDP-11 Extended Instruction Set • FP11 floating point • PDP-11 Memory Management |

| UNIBUS CPUs: KA11 • KC11 • KB11-A • KB11-B • KB11-C • KB11-D • KD11-A • KD11-B • KD11-D • KD11-E • KD11-EA • KD11-K • KD11-Z • KDF11-U

Co-processors: FP11-A • FP11-B • FP11-C • FP11-E • FP11-F • KE44-A • FPF11 Chips: LSI-11 • KEV11-A • KEV11-B • KEV11-C • F-11 • KEF11-A • KTF11-A • T-11 • J-11 • FPJ11 CPU options: KE11-E • KE11-F • KJ11-A • KT11-C • KT11-D • KK11-A • KK11-B • KT24 • KTJ11-B Rare CPU options: KS11 Memory Protection and Relocation option • KT11-B Paging Option • KUV11 Writeable Control Store Front panels: KY11-A • KY11-D • KY11-J • KY11-LA • KY11-LB • KY11-P More on buses: UNIBUS and QBUS termination • Bus Arbitration on the Unibus and QBUS • CTI BUS PDT-11s - PDT-11/110 • PDT-11/130 • PDT-11/150 CTI PDP-11s - PRO-325 • PRO-350 • PRO-380 Other: FIS floating point • PDP-11 Commercial Instruction Set • PDP-11 stacks • PDP-11 family differences |