Difference between revisions of "MM11-D core memory"

m (+cat) |

(+img) |

||

| Line 1: | Line 1: | ||

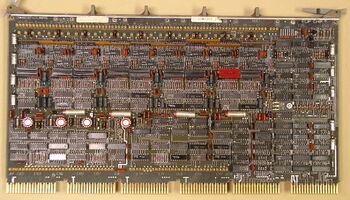

| − | The '''MM11-D''' was a 32 Kbyte [[core memory|core]] [[main memory]] for | + | [[Image:MM11-DFront.jpg|350px|thumb|right|MM11-D set, showing the G652 mother-board]] |

| + | |||

| + | The '''MM11-D''' was a 32 Kbyte [[core memory|core]] [[main memory]] for [[PDP-11]] [[UNIBUS]] machines. An MM11-D was composed of two [[DEC card form factor|hex]] boards, one piggy-backed on the other, and the pair taking only a single [[backplane]] slot (electrically): | ||

* An H222-A daughter-board containing the cores | * An H222-A daughter-board containing the cores | ||

| − | * A G652 mother-board containing most of the electronics, and the contact fingers for plugging into a [[backplane]] | + | * A G652 mother-board containing most of the electronics, and the contact fingers for plugging into a [[backplane]] slot |

The MM11-D did not use a custom backplane; it plugged into a standard [[Modified UNIBUS Device|MUD slot]]. The pair was 'thick' enough that a normal board cannot be plugged into the next slot; instead, a [[G727 grant continuity card]] must be used there (since it has no components on it, it just clears the H222-A card). | The MM11-D did not use a custom backplane; it plugged into a standard [[Modified UNIBUS Device|MUD slot]]. The pair was 'thick' enough that a normal board cannot be plugged into the next slot; instead, a [[G727 grant continuity card]] must be used there (since it has no components on it, it just clears the H222-A card). | ||

| − | There was also a parity-capable variant, the '''MM11-DP''', which | + | There was also a parity-capable variant, the '''MM11-DP''', which used an M7850 parity controller plugged into the same backplane as the MM11-D, and substituted a core array with two more bits per word. |

| − | It is possible to [[interleave]] a pair of MM11-D's to provide reduced effective average [[access time]]s. | + | It is possible to [[interleaving|interleave]] a pair of MM11-D's to provide reduced effective average [[access time]]s. |

==Configuration== | ==Configuration== | ||

Revision as of 11:43, 7 October 2021

The MM11-D was a 32 Kbyte core main memory for PDP-11 UNIBUS machines. An MM11-D was composed of two hex boards, one piggy-backed on the other, and the pair taking only a single backplane slot (electrically):

- An H222-A daughter-board containing the cores

- A G652 mother-board containing most of the electronics, and the contact fingers for plugging into a backplane slot

The MM11-D did not use a custom backplane; it plugged into a standard MUD slot. The pair was 'thick' enough that a normal board cannot be plugged into the next slot; instead, a G727 grant continuity card must be used there (since it has no components on it, it just clears the H222-A card).

There was also a parity-capable variant, the MM11-DP, which used an M7850 parity controller plugged into the same backplane as the MM11-D, and substituted a core array with two more bits per word.

It is possible to interleave a pair of MM11-D's to provide reduced effective average access times.

Configuration

The DEC manuals for the MM11-D list the jumpers used to configure the MM11-D, but they do not show their location, and the board does not contain captions for the jumpers.

They are on the G652 board, on the center right (with the board upright, with the contact fingers at the bottom). W1 is the jumper on the right (toward the edge of the board), and W8 is the one on the left (toward the center of the board), with the others in order between them.

| v • d • e PDP-11 Computers and Peripherals |

|---|

| UNIBUS PDP-11s - PDP-11/20 • PDP-11/15 • PDP-11/35 • PDP-11/40 • PDP-11/45 • PDP-11/50 • PDP-11/55 • PDP-11/70 PDP-11/05 • PDP-11/10 • PDP-11/04 • PDP-11/34 • PDP-11/60 • PDP-11/44 • PDP-11/24 • PDP-11/84 • PDP-11/94 QBUS PDP-11s - PDP-11/03 • PDP-11/23 • PDP-11/23+ • MicroPDP-11/73 • MicroPDP-11/53 • MicroPDP-11/83 • MicroPDP-11/93 QBUS CPUs: LSI-11 • LSI-11/2 • KDF11-A • KDF11-B • KDJ11-A • KDJ11-B • KDJ11-D • KDJ11-E Buses: UNIBUS • UNIBUS map • SPC • MUD • EUB • QBUS • CD interconnect • PMI Also: PDP-11 architecture • PDP-11 Extended Instruction Set • FP11 floating point • PDP-11 Memory Management |

| UNIBUS CPUs: KA11 • KC11 • KB11-A • KB11-B • KB11-C • KB11-D • KD11-A • KD11-B • KD11-D • KD11-E • KD11-EA • KD11-K • KD11-Z • KDF11-U

Co-processors: FP11-A • FP11-B • FP11-C • FP11-E • FP11-F • KE44-A • FPF11 Chips: LSI-11 • KEV11-A • KEV11-B • KEV11-C • F-11 • KEF11-A • KTF11-A • T-11 • J-11 • FPJ11 CPU options: KE11-E • KE11-F • KJ11-A • KT11-C • KT11-D • KK11-A • KK11-B • KT24 • KTJ11-B Rare CPU options: KS11 Memory Protection and Relocation option • KT11-B Paging Option • KUV11 Writeable Control Store Front panels: KY11-A • KY11-D • KY11-J • KY11-LA • KY11-LB • KY11-P More on buses: UNIBUS and QBUS termination • Bus Arbitration on the Unibus and QBUS • CTI BUS PDT-11s - PDT-11/110 • PDT-11/130 • PDT-11/150 CTI PDP-11s - PRO-325 • PRO-350 • PRO-380 Other: FIS floating point • PDP-11 Commercial Instruction Set • PDP-11 stacks • PDP-11 family differences |