Difference between revisions of "PDP-11/05"

m (→Control PROMs: possible mis-print?) |

(Move image into infobox) |

||

| (20 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

| − | |||

| − | |||

{{Infobox Machine | {{Infobox Machine | ||

| name = PDP-11/05 | | name = PDP-11/05 | ||

| − | | manufacturer = [[Digital Equipment Corporation]] | + | | image = pdp11-05.jpg |

| − | | architecture = [[PDP-11]] | + | | imgwidth = 200px |

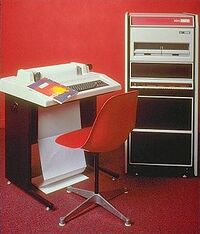

| + | | caption = A PDP-11/05 in a 'low-boy' rack, from a sales brochure | ||

| + | | manufacturer = [[Digital Equipment Corporation|DEC]] | ||

| + | | architecture = [[PDP-11 architecture|PDP-11]] | ||

| word size= 16 bit | | word size= 16 bit | ||

| − | | physical address= 18 | + | | physical address= 18 bits (only 16 bits usable) |

| year introduced= June 1972 | | year introduced= June 1972 | ||

| bus arch = [[UNIBUS]] | | bus arch = [[UNIBUS]] | ||

}} | }} | ||

| + | The '''PDP-11/05''' was the fourth model in the [[PDP-11]] series, following the [[PDP-11/20]], the [[PDP-11/45]] and the [[PDP-11/40]]; it used the [[KD11-B CPU]]. It was intended as a cost-reduced low-end machine to replace the PDP-11/20. Like all the other early PDP-11's, it was a [[UNIBUS]] machine. | ||

| − | + | The PDP-11/05 was absolutely identical to the [[PDP-11/10]]; the only difference between the /05 and the /10 was the number printed on the [[front panel]] (the [[KY11-J Programmer's Console]]). The /05 was aimed toward the [[Original Equipment Manufacturer|OEM]] market, while the /10 was intended for [[end-user]]s. General usage (following DEC's lead) is to refer to all these machines as '11/05's. | |

| − | | | ||

| − | The | + | The earliest units came in a 5-1/4" box, which had room for only a double [[system unit]] [[backplane]]. (Additional memory was initially indicated to require the use of an [[MM11-L core memory|ME11-L]] memory unit; similarly, a [[BA11-E Mounting Box]] was initially indicated as required to hold any [[device controller]]s beyond the limited number the [[Central Processing Unit|CPU]] backplane would hold. Alternative solutions to both were of course possible.) The [[power supply]] of this box does not have an 'Hxxx' assembly identifier, only a [[DEC part number]]: 70-08731; and 54-09728 for the DC Regulator Module. |

| − | + | A later version, the /05N and /10N, came in a 10-1/2" [[BA11-D Mounting Box]]; the final /05S and /10S versions came in the 10-1/2" [[BA11-K Mounting Box]]. | |

| − | |||

| − | |||

==Backplane versions== | ==Backplane versions== | ||

| − | The PDP-11/05 and /10 came in three versions, with different main | + | The PDP-11/05 and /10 came in three versions, with four different versions of the main backplane (the 9-slot system unit holding the two CPU cards). All have two [[DEC card form factor|single-height]] slot sections for the [[KM11-A Maintenance Set|KM11 card]], plugged in to debug the CPU; each slot is numbered with the correct KD11-B KM11 overlay for a KM11 in that slot. (The KM11 switches function identically in both slots.) |

| − | + | ===Original version=== | |

| − | + | The original /05 and /10 came with backplanes wired to hold [[MM11-L core memory|MM11-L]] 16 Kbyte [[core memory]] units. There were two different backplanes (all four backplanes are un-named, but the part numbers, given below, are etched into the large [[printed circuit board|PCB]] on each). | |

| − | + | One, (called "Configuration 1" in [[Digital Equipment Corporation|DEC]] documentation, backplane part #54-10035), held two memory units, with one slot left for quad-height [[Small Peripheral Controller|SPC]] devices. The other ("Configuration 2", backplane part #54-09818) held one memory unit, and provided four SPC slots; it could also hold a [[DF11 Communications Line Adapter]] to convert the [[asynchronous serial line]] console line to [[EIA RS-232 serial line interface|EIA RS-232]]. | |

| − | + | Here are the slot assignments in the backplanes (as seen from the board insertion side of the backplane, not the [[wire-wrap]] pin side, as is common in DEC documentation) : | |

| − | + | Configuration 1: | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

{| class="wikitable" | {| class="wikitable" | ||

| − | ! | + | ! !! colspan="6" | Connector |

| − | |||

| − | |||

|- | |- | ||

| − | + | ! Slot !! A !! B !! C !! D !! E !! F | |

|- | |- | ||

| − | | | + | | 1 || colspan="6" style="text-align:center;" | M7260 CPU board #0 |

|- | |- | ||

| − | | | + | | 2 || colspan="6" style="text-align:center;" | M7261 CPU board #1 |

|- | |- | ||

| − | | | + | | 3 || colspan="6" style="text-align:center;" | G110 Memory Control |

|- | |- | ||

| − | | | + | | 4 || colspan="6" style="text-align:center;" | G231 Memory Driver |

|- | |- | ||

| − | | | + | | 5 || colspan="2" | UNIBUS Terminator || colspan="4" | H213/H214 Core stack |

|- | |- | ||

| − | | | + | | 6 || colspan="6" style="text-align:center;" | G110 Memory Control |

|- | |- | ||

| − | | | + | | 7 || colspan="6" style="text-align:center;" | G231 Memory Driver |

|- | |- | ||

| − | | | + | | 8 || colspan="2" | UNIBUS Out || colspan="4" | H213/H214 Core stack |

|- | |- | ||

| − | | | + | | 9 || KM11-1 || KM11-2 || colspan="4" style="text-align:center;" | SPC |

|} | |} | ||

| − | + | Configuration 2: | |

{| class="wikitable" | {| class="wikitable" | ||

| − | ! | + | ! !! colspan="6" | Connector |

|- | |- | ||

| − | + | ! Slot !! A !! B !! C !! D !! E !! F | |

|- | |- | ||

| − | | | + | | 1 || colspan="6" style="text-align:center;" | M7260 CPU board #0 |

|- | |- | ||

| − | | | + | | 2 || colspan="6" style="text-align:center;" | M7261 CPU board #1 |

|- | |- | ||

| − | | | + | | 3 || colspan="6" style="text-align:center;" | G110 Memory Control |

|- | |- | ||

| − | | | + | | 4 || colspan="6" style="text-align:center;" | G231 Memory Driver |

|- | |- | ||

| − | | | + | | 5 || colspan="2" | UNIBUS Terminator || colspan="4" | H213/H214 Core stack |

|- | |- | ||

| − | | | + | | 6 || colspan="2" | Unused || colspan="4" style="text-align:center;" | SPC |

|- | |- | ||

| − | | | + | | 7 || colspan="2" | UNIBUS Out || colspan="4" style="text-align:center;" | SPC |

|- | |- | ||

| − | | | + | | 8 || KM11-1 || KM11-2 || colspan="4" style="text-align:center;" | SPC |

|- | |- | ||

| − | | | + | | 9 || colspan="2" | DF11 || colspan="4" style="text-align:center;" | SPC |

| + | |} | ||

| + | |||

| + | Note that the slots are numbered from 1 at the start; this is the inverse of the numbering for these backplanes in some DEC documentation. | ||

| + | |||

| + | ===-N type=== | ||

| + | |||

| + | The /05N and /10N had a slightly different backplane (part #54-10329; the complete unit has been observed labelled "Type: 10 5K", "Part No.: 70-09241"). This had space for two MM11-L memory units, but deleted the SPC slot of the previous double MM11-L backplane, and replaced it with a slot to hold the dual-height M9970 console terminal cable board, and also a dual-height DF11. | ||

| + | |||

| + | Board locations (again, as seen from the board insertion side of the backplane) are: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! !! colspan="6" | Connector | ||

|- | |- | ||

| − | + | ! Slot !! A !! B !! C !! D !! E !! F | |

|- | |- | ||

| − | | | + | | 1 || colspan="2" | DF11 || colspan="2" | M9970 || KM11-A || KM11-B |

|- | |- | ||

| − | | | + | | 2 || colspan="6" style="text-align:center;" | M7260 CPU board #0 |

|- | |- | ||

| − | | | + | | 3 || colspan="6" style="text-align:center;" | M7261 CPU board #1 |

|- | |- | ||

| − | | | + | | 4 || colspan="2" | UNIBUS Terminator || colspan="4" | H213/H214 Core stack |

|- | |- | ||

| − | | | + | | 5 || colspan="6" style="text-align:center;" | G110 Memory Control |

|- | |- | ||

| − | | | + | | 6 || colspan="6" style="text-align:center;" | G231 Memory Driver |

|- | |- | ||

| − | | | + | | 7 || colspan="6" style="text-align:center;" | G110 Memory Control |

|- | |- | ||

| − | | | + | | 8 || colspan="6" style="text-align:center;" | G231 Memory Driver |

|- | |- | ||

| − | | | + | | 9 || colspan="2" | UNIBUS Out || colspan="4" | H213/H214 Core stack |

| − | |||

| − | |||

| − | |||

| − | |||

|} | |} | ||

| − | '' | + | Note that the two KM11 slots are at the other side of the backplane from the slots used for them in the 'Configuration 1' and 'Configuration 2' backplanes. |

| − | + | ===-S type=== | |

| − | + | The /05S and /10S came with a backplane (part #54-10972, complete assembly part #70-09921) wired to hold an [[MM11-U core memory|MM11-U]] 32 Kbyte core memory, and which provided three SPC slots. The layout (from the board insertion side) is: | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

{| class="wikitable" | {| class="wikitable" | ||

| − | ! | + | ! !! colspan="6" | Connector |

|- | |- | ||

| − | + | ! Slot !! A !! B !! C !! D !! E !! F | |

|- | |- | ||

| − | | | + | | 1 || colspan="6" style="text-align:center;" | M7260 CPU board #0 |

|- | |- | ||

| − | | | + | | 2 || colspan="6" style="text-align:center;" | M7261 CPU board #1 |

|- | |- | ||

| − | | | + | | 3 || colspan="2" | UNIBUS Terminator || colspan="4" style="text-align:center;" | SPC |

| + | |- | ||

| + | | 4 || colspan="2" | DF11 or M9970 || colspan="4" style="text-align:center;" | SPC | ||

| + | |- | ||

| + | | 5 || KM11-1 || KM11-2 || colspan="4" style="text-align:center;" | SPC | ||

| + | |- | ||

| + | | 6 || colspan="6" style="text-align:center;" | G235 X-Y Drive | ||

| + | |- | ||

| + | | 7 || colspan="6" style="text-align:center;" | H217-D Core Stack | ||

| + | |- | ||

| + | | 8 || colspan="6" style="text-align:center;" | G114 Sense/Inhibit | ||

| + | |- | ||

| + | | 9 || colspan="2" | UNIBUS Out || colspan="4" style="text-align:center;" | M8293 Memory Control | ||

|} | |} | ||

==Keys== | ==Keys== | ||

| − | Unlike all the other PDP-11s, which use a | + | Unlike all the other keyed PDP-11s, which use a cylindrical Ace key, the /05's (and /10s) use a normal flat Yale-type key. The original key is a Chicago Lock Company key, code "GRB 2"; this is cut 215, on a Chicago K5K or Ilco S1041T blank. (It has been confirmed that a locksmith was able to produce a working key from this information.) If simply duplicating an existing key, Hillman Y11 and FR4 blanks may be used (both work, but one has to be trimmed a bit, length-wise). |

| − | one has to be trimmed a bit, length-wise). | ||

| − | == Gallery == | + | ==Gallery== |

[[Image:PDP1105.jpg|150px]] | [[Image:PDP1105.jpg|150px]] | ||

[[Image:1105.jpg|150px]] | [[Image:1105.jpg|150px]] | ||

| − | {{PDP-11}} | + | ==External links== |

| + | |||

| + | * [http://www.bitsavers.org/pdf/dec/pdp11/1105/ PDP-11/05] - BitSavers | ||

| + | ** [http://bitsavers.org/pdf/dec/pdp11/1105/DEC-11-H05AA-A-D_1105um.pdf PDP-11/05 computer manual] (DEC-11-H05AA-A-D) - covers the initial 5-1/4 inch box version; the power supply is covered in ''Part IV: Power Supply'' (pp. 276-313 of the PDF) | ||

| + | ** [http://www.bitsavers.org/www.computer.museum.uq.edu.au/pdf/DEC-11-H05AA-B-D%20PDP-11-05,%2011-10%20Computer%20Manual.pdf PDP-11/05, 11/10 computer manual] (DEC-11-H05AA-B-D) - also covers the first 10-1/2" box version, in ''Supplement 1: PDP-11/05, 11/10 10 1/2 inch mounting box and power system'' (pp. 291-372 of the PDF) | ||

| + | ** [http://www.bitsavers.org/pdf/dec/pdp11/1105/1105_RevAH_Engineering_Drawings_Jul76.pdf 16 bit computer (PDP 1105) engineering drawings] - covers the 5-1/4" box, and the first 10-1/2" box version (doesn't seem to have the 5-1/4" box power supply, though) | ||

| + | ** [http://www.bitsavers.org/pdf/dec/pdp11/1105/1105S_Schem.pdf PDP-11/05-S, 11/10-S systems engineering drawings] | ||

| + | * [https://vt100.net/mirror/hcps/h05ssbd.pdf PDP-11/05-S, 11/10-S system manual] (DEC-11-H05SS-B-D) - covers the second 10-1/2" box version | ||

| + | * [http://www.vaxhaven.com/images/7/76/EK-11005-TM-003.pdf PDP-11/05, 11/10 computer manual] (EK-11005-TM-003) - does not cover the later 10-1/2" box version; covers the first version in Chapters 17-19 (pp. 154-216 of the PDF) | ||

| + | |||

| + | {{Nav PDP-11}} | ||

| − | + | [[Category:UNIBUS PDP-11s]] | |

| − | [[Category:UNIBUS | ||

Latest revision as of 17:18, 8 February 2024

| PDP-11/05 | |

A PDP-11/05 in a 'low-boy' rack, from a sales brochure | |

| Manufacturer: | DEC |

|---|---|

| Architecture: | PDP-11 |

| Year Introduced: | June 1972 |

| Word Size: | 16 bit |

| Physical Address Size: | 18 bits (only 16 bits usable) |

| Bus Architecture: | UNIBUS |

The PDP-11/05 was the fourth model in the PDP-11 series, following the PDP-11/20, the PDP-11/45 and the PDP-11/40; it used the KD11-B CPU. It was intended as a cost-reduced low-end machine to replace the PDP-11/20. Like all the other early PDP-11's, it was a UNIBUS machine.

The PDP-11/05 was absolutely identical to the PDP-11/10; the only difference between the /05 and the /10 was the number printed on the front panel (the KY11-J Programmer's Console). The /05 was aimed toward the OEM market, while the /10 was intended for end-users. General usage (following DEC's lead) is to refer to all these machines as '11/05's.

The earliest units came in a 5-1/4" box, which had room for only a double system unit backplane. (Additional memory was initially indicated to require the use of an ME11-L memory unit; similarly, a BA11-E Mounting Box was initially indicated as required to hold any device controllers beyond the limited number the CPU backplane would hold. Alternative solutions to both were of course possible.) The power supply of this box does not have an 'Hxxx' assembly identifier, only a DEC part number: 70-08731; and 54-09728 for the DC Regulator Module.

A later version, the /05N and /10N, came in a 10-1/2" BA11-D Mounting Box; the final /05S and /10S versions came in the 10-1/2" BA11-K Mounting Box.

Contents

Backplane versions

The PDP-11/05 and /10 came in three versions, with four different versions of the main backplane (the 9-slot system unit holding the two CPU cards). All have two single-height slot sections for the KM11 card, plugged in to debug the CPU; each slot is numbered with the correct KD11-B KM11 overlay for a KM11 in that slot. (The KM11 switches function identically in both slots.)

Original version

The original /05 and /10 came with backplanes wired to hold MM11-L 16 Kbyte core memory units. There were two different backplanes (all four backplanes are un-named, but the part numbers, given below, are etched into the large PCB on each).

One, (called "Configuration 1" in DEC documentation, backplane part #54-10035), held two memory units, with one slot left for quad-height SPC devices. The other ("Configuration 2", backplane part #54-09818) held one memory unit, and provided four SPC slots; it could also hold a DF11 Communications Line Adapter to convert the asynchronous serial line console line to EIA RS-232.

Here are the slot assignments in the backplanes (as seen from the board insertion side of the backplane, not the wire-wrap pin side, as is common in DEC documentation) :

Configuration 1:

| Connector | ||||||

|---|---|---|---|---|---|---|

| Slot | A | B | C | D | E | F |

| 1 | M7260 CPU board #0 | |||||

| 2 | M7261 CPU board #1 | |||||

| 3 | G110 Memory Control | |||||

| 4 | G231 Memory Driver | |||||

| 5 | UNIBUS Terminator | H213/H214 Core stack | ||||

| 6 | G110 Memory Control | |||||

| 7 | G231 Memory Driver | |||||

| 8 | UNIBUS Out | H213/H214 Core stack | ||||

| 9 | KM11-1 | KM11-2 | SPC | |||

Configuration 2:

| Connector | ||||||

|---|---|---|---|---|---|---|

| Slot | A | B | C | D | E | F |

| 1 | M7260 CPU board #0 | |||||

| 2 | M7261 CPU board #1 | |||||

| 3 | G110 Memory Control | |||||

| 4 | G231 Memory Driver | |||||

| 5 | UNIBUS Terminator | H213/H214 Core stack | ||||

| 6 | Unused | SPC | ||||

| 7 | UNIBUS Out | SPC | ||||

| 8 | KM11-1 | KM11-2 | SPC | |||

| 9 | DF11 | SPC | ||||

Note that the slots are numbered from 1 at the start; this is the inverse of the numbering for these backplanes in some DEC documentation.

-N type

The /05N and /10N had a slightly different backplane (part #54-10329; the complete unit has been observed labelled "Type: 10 5K", "Part No.: 70-09241"). This had space for two MM11-L memory units, but deleted the SPC slot of the previous double MM11-L backplane, and replaced it with a slot to hold the dual-height M9970 console terminal cable board, and also a dual-height DF11.

Board locations (again, as seen from the board insertion side of the backplane) are:

| Connector | ||||||

|---|---|---|---|---|---|---|

| Slot | A | B | C | D | E | F |

| 1 | DF11 | M9970 | KM11-A | KM11-B | ||

| 2 | M7260 CPU board #0 | |||||

| 3 | M7261 CPU board #1 | |||||

| 4 | UNIBUS Terminator | H213/H214 Core stack | ||||

| 5 | G110 Memory Control | |||||

| 6 | G231 Memory Driver | |||||

| 7 | G110 Memory Control | |||||

| 8 | G231 Memory Driver | |||||

| 9 | UNIBUS Out | H213/H214 Core stack | ||||

Note that the two KM11 slots are at the other side of the backplane from the slots used for them in the 'Configuration 1' and 'Configuration 2' backplanes.

-S type

The /05S and /10S came with a backplane (part #54-10972, complete assembly part #70-09921) wired to hold an MM11-U 32 Kbyte core memory, and which provided three SPC slots. The layout (from the board insertion side) is:

| Connector | ||||||

|---|---|---|---|---|---|---|

| Slot | A | B | C | D | E | F |

| 1 | M7260 CPU board #0 | |||||

| 2 | M7261 CPU board #1 | |||||

| 3 | UNIBUS Terminator | SPC | ||||

| 4 | DF11 or M9970 | SPC | ||||

| 5 | KM11-1 | KM11-2 | SPC | |||

| 6 | G235 X-Y Drive | |||||

| 7 | H217-D Core Stack | |||||

| 8 | G114 Sense/Inhibit | |||||

| 9 | UNIBUS Out | M8293 Memory Control | ||||

Keys

Unlike all the other keyed PDP-11s, which use a cylindrical Ace key, the /05's (and /10s) use a normal flat Yale-type key. The original key is a Chicago Lock Company key, code "GRB 2"; this is cut 215, on a Chicago K5K or Ilco S1041T blank. (It has been confirmed that a locksmith was able to produce a working key from this information.) If simply duplicating an existing key, Hillman Y11 and FR4 blanks may be used (both work, but one has to be trimmed a bit, length-wise).

Gallery

External links

- PDP-11/05 - BitSavers

- PDP-11/05 computer manual (DEC-11-H05AA-A-D) - covers the initial 5-1/4 inch box version; the power supply is covered in Part IV: Power Supply (pp. 276-313 of the PDF)

- PDP-11/05, 11/10 computer manual (DEC-11-H05AA-B-D) - also covers the first 10-1/2" box version, in Supplement 1: PDP-11/05, 11/10 10 1/2 inch mounting box and power system (pp. 291-372 of the PDF)

- 16 bit computer (PDP 1105) engineering drawings - covers the 5-1/4" box, and the first 10-1/2" box version (doesn't seem to have the 5-1/4" box power supply, though)

- PDP-11/05-S, 11/10-S systems engineering drawings

- PDP-11/05-S, 11/10-S system manual (DEC-11-H05SS-B-D) - covers the second 10-1/2" box version

- PDP-11/05, 11/10 computer manual (EK-11005-TM-003) - does not cover the later 10-1/2" box version; covers the first version in Chapters 17-19 (pp. 154-216 of the PDF)

| v • d • e PDP-11 Computers and Peripherals |

|---|

| UNIBUS PDP-11s - PDP-11/20 • PDP-11/15 • PDP-11/35 • PDP-11/40 • PDP-11/45 • PDP-11/50 • PDP-11/55 • PDP-11/70 PDP-11/05 • PDP-11/10 • PDP-11/04 • PDP-11/34 • PDP-11/60 • PDP-11/44 • PDP-11/24 • PDP-11/84 • PDP-11/94 QBUS PDP-11s - PDP-11/03 • PDP-11/23 • PDP-11/23+ • MicroPDP-11/73 • MicroPDP-11/53 • MicroPDP-11/83 • MicroPDP-11/93 QBUS CPUs: LSI-11 • LSI-11/2 • KDF11-A • KDF11-B • KDJ11-A • KDJ11-B • KDJ11-D • KDJ11-E Buses: UNIBUS • UNIBUS map • SPC • MUD • EUB • QBUS • CD interconnect • PMI Also: PDP-11 architecture • PDP-11 Extended Instruction Set • FP11 floating point • PDP-11 Memory Management |

| UNIBUS CPUs: KA11 • KC11 • KB11-A • KB11-B • KB11-C • KB11-D • KD11-A • KD11-B • KD11-D • KD11-E • KD11-EA • KD11-K • KD11-Z • KDF11-U

Co-processors: FP11-A • FP11-B • FP11-C • FP11-E • FP11-F • KE44-A • FPF11 Chips: LSI-11 • KEV11-A • KEV11-B • KEV11-C • F-11 • KEF11-A • KTF11-A • T-11 • J-11 • FPJ11 CPU options: KE11-E • KE11-F • KJ11-A • KT11-C • KT11-D • KK11-A • KK11-B • KT24 • KTJ11-B Rare CPU options: KS11 Memory Protection and Relocation option • KT11-B Paging Option • KUV11 Writeable Control Store Front panels: KY11-A • KY11-D • KY11-J • KY11-LA • KY11-LB • KY11-P More on buses: UNIBUS and QBUS termination • Bus Arbitration on the Unibus and QBUS • CTI BUS PDT-11s - PDT-11/110 • PDT-11/130 • PDT-11/150 CTI PDP-11s - PRO-325 • PRO-350 • PRO-380 Other: FIS floating point • PDP-11 Commercial Instruction Set • PDP-11 stacks • PDP-11 family differences |