Difference between revisions of "PDP-11/70"

(Link a few terms) |

m (→External links: +pdp11 processor handbook) |

||

| (11 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

| − | |||

| − | |||

{{Infobox Machine | {{Infobox Machine | ||

| − | | name=PDP-11/70 | + | | image= pdp11-70.jpg |

| − | | manufacturer=[[Digital Equipment Corporation]] | + | | caption= A PDP-11/70 |

| + | | name= PDP-11/70 | ||

| + | | manufacturer= [[Digital Equipment Corporation]] | ||

| word size= 16 bit | | word size= 16 bit | ||

| virtual address= 16 bit | | virtual address= 16 bit | ||

| Line 9: | Line 9: | ||

| bus arch= [[UNIBUS]]/[[MASSBUS]]/memory bus | | bus arch= [[UNIBUS]]/[[MASSBUS]]/memory bus | ||

| year introduced= March 1975 | | year introduced= March 1975 | ||

| − | |||

|}} | |}} | ||

| − | The '''PDP-11/70''' was a very high performance [[UNIBUS]] [[PDP-11]] system; it basically took the high-performance CPU of the [[PDP-11/45]] (implemented in [[SSI]] [[Schottky TTL]] logic), and augmented it with: | + | The '''PDP-11/70''' was a very high performance [[UNIBUS]] [[PDP-11]] system; it basically took the high-performance [[Central Processing Unit|CPU]] of the [[PDP-11/45]] (implemented in [[SSI]] [[Schottky TTL]] logic), and augmented it with: |

* A 2 Kbyte, 300 nsec [[cache]], organized as 2-way set associative, with 4-byte blocks, connected to what had been the FastBus high-speed memory interface on the PDP-11/45 CPU | * A 2 Kbyte, 300 nsec [[cache]], organized as 2-way set associative, with 4-byte blocks, connected to what had been the FastBus high-speed memory interface on the PDP-11/45 CPU | ||

| − | * The ability to support up to 4 Mbytes of memory via a new Main Memory Bus, and changes to the CPU to allow access to that much memory | + | * The ability to support up to 4 Mbytes of [[main memory]] via a new Main Memory Bus, and changes to the CPU to allow access to that much memory |

* A [[UNIBUS map]] to allow devices on the UNIBUS access to all of that memory | * A [[UNIBUS map]] to allow devices on the UNIBUS access to all of that memory | ||

| − | * The ability to support up to 4 [[MASSBUS]] | + | * The ability to support up to 4 [[RH70 MASSBUS controller]]s, which connected high-speed [[secondary storage]] devices directly to the main memory, bypassing the UNIBUS |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | The CPU was the [[KB11-B CPU|KB11-B]] (in early units, prior to 1976) or [[KB11-C CPU|KB11-C]] (later) CPU. (The difference between the two was whether they took the optional [[FP11-B Floating-Point Processor|FP11-B]] or [[FP11-C Floating-Point Processor|FP11-C]] [[Floating point processor|FPP]].) | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | == | + | ==Main memory== |

| − | The | + | The main memory systems supported by the -11/70 were the [[MJ11 memory system]] (which used [[core memory]]), and the later [[MK11 memory system]] (which used [[dynamic RAM]]). |

| − | + | The Main Memory Bus consisted of [[transmission line]]s, which required [[terminator]]s on both ends; at the MJ11/MK11 end, a pair of H873 modules were plugged into the last output port, to do that. | |

| − | |||

| − | + | The cabling used for the Main Memory Bus ([[DEC part number]] 70-10824) consists of a set of four BC06R-xx [[flat cable]]s; two for the [[address]] and control, and two for the data. They run from [[Berg connector]] headers on boards in the KB11 CPU's cache to others on boards in the MJ11/MK11. | |

== hampage.hu == | == hampage.hu == | ||

| Line 71: | Line 46: | ||

[[Image:pdp11_70b.jpg|200px]] | [[Image:pdp11_70b.jpg|200px]] | ||

[[Image:pdp11-70c.jpg|200px]] | [[Image:pdp11-70c.jpg|200px]] | ||

| − | {{stub}} | + | |

| + | ==Further reading== | ||

| + | |||

| + | * ''PDP-11/70 maintenance and installation manual'', EK-11070-MM-002 | ||

| + | |||

| + | == External links == | ||

| + | |||

| + | * [http://bitsavers.org/pdf/dec/pdp11/1170/ 11/70] - documentation at [[Bitsavers]] | ||

| + | ** [http://bitsavers.org/pdf/dec/pdp11/1170/PDP-11_70_Handbook_1977-78.pdf pdp11/70 processor handbook (1977-78)] | ||

| + | ** [http://bitsavers.org/pdf/dec/pdp11/1170/EK-11070-MM-002_May79.pdf PDP-11/70 maintenance and installation manual] (EK-11070-MM-002) | ||

| + | ** [http://bitsavers.org/pdf/dec/pdp11/1170/KA-K1170-MG-003_1170_Maintenance_Service_Guide_Apr88.pdf 1170 Maintenance Service Guide] (KA-K1170-MG-003) | ||

| + | ** [http://bitsavers.org/pdf/dec/pdp11/1170/1170_StudentHandouts.pdf PDP-11/70 Hardware Student Handouts] | ||

| + | ** [http://bitsavers.org/pdf/dec/pdp11/1170/1170_Engineering_Drawings_revL_Mar1977.pdf 11/70 Engineering Drawings] | ||

| + | * [http://www.bitsavers.org/pdf/dec/pdp11/handbooks/PDP-11_Processor_Handbook_1981.pdf pdp11 processor handbook - pdp11/04/24/34A/44/70] | ||

| + | * [http://avitech.com.au/?page_id=366 PDP-11/70] - contains many good images | ||

| + | * [http://obsolescence.wixsite.com/obsolescence/pidp-11 PiDP-11: a functional scale model replica of the PDP-11/70 console] | ||

| + | |||

| + | {{semi-stub}} | ||

{{PDP-11}} | {{PDP-11}} | ||

| − | [[Category:UNIBUS PDP-11s]] | + | [[Category: UNIBUS PDP-11s]] |

Latest revision as of 21:43, 29 February 2024

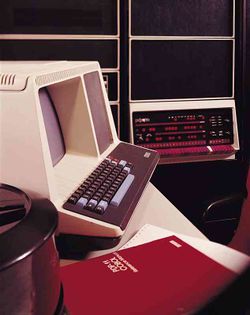

| PDP-11/70 | |

A PDP-11/70 | |

| Manufacturer: | Digital Equipment Corporation |

|---|---|

| Year Introduced: | March 1975 |

| Word Size: | 16 bit |

| Physical Address Size: | 22 bit |

| Virtual Address Size: | 16 bit |

| Bus Architecture: | UNIBUS/MASSBUS/memory bus |

The PDP-11/70 was a very high performance UNIBUS PDP-11 system; it basically took the high-performance CPU of the PDP-11/45 (implemented in SSI Schottky TTL logic), and augmented it with:

- A 2 Kbyte, 300 nsec cache, organized as 2-way set associative, with 4-byte blocks, connected to what had been the FastBus high-speed memory interface on the PDP-11/45 CPU

- The ability to support up to 4 Mbytes of main memory via a new Main Memory Bus, and changes to the CPU to allow access to that much memory

- A UNIBUS map to allow devices on the UNIBUS access to all of that memory

- The ability to support up to 4 RH70 MASSBUS controllers, which connected high-speed secondary storage devices directly to the main memory, bypassing the UNIBUS

The CPU was the KB11-B (in early units, prior to 1976) or KB11-C (later) CPU. (The difference between the two was whether they took the optional FP11-B or FP11-C FPP.)

Main memory

The main memory systems supported by the -11/70 were the MJ11 memory system (which used core memory), and the later MK11 memory system (which used dynamic RAM).

The Main Memory Bus consisted of transmission lines, which required terminators on both ends; at the MJ11/MK11 end, a pair of H873 modules were plugged into the last output port, to do that.

The cabling used for the Main Memory Bus (DEC part number 70-10824) consists of a set of four BC06R-xx flat cables; two for the address and control, and two for the data. They run from Berg connector headers on boards in the KB11 CPU's cache to others on boards in the MJ11/MK11.

hampage.hu

Quote: Introduced in March 1975, the PDP-11/70 is the bigest of the PDP-11s. The KB11B is a re-enginered version of the PDP-11/45's CPU, with some new features. Two of the most important changes was the addition of cache (2 KByte of bipolar memory) and the 22-bit memory management. The latter enables the usage of memory up to 2 Mwords, using the UNIBUS map, which translates 18-bit UNIBUS addresses to 22-bit physical addresses. The kernel/supervisor/user operating modes and the MMU was standard. Important options: FPP, MASSBUS adapters (RH70's, up to four) with direct memory access.

The original processor had the floating point unit of the PDP-11/45, which turned out to be ineffective, so it was resdesigned (KB11C). Overall performance is 0.6th of the VAX-11/780.

A normal system occupied at least two H960 cabinets (memory and CPU), the UNIBUS expansion needed another. There were also later revisions sold in another cabinet, without the front panel (Datasystem 570?).

Trivia: The original business plan called for 1000 PDP-11/70's to be built, it was supposed to be a "stopgap" until the "wide word machine" came out. This "word wide machine" was originally a small PDP-10 (36-bit machine), but it was then cancelled in favor of the 32-bit VAX. Anyhow, more than 10,000 PDP-11/70's were built.

Gallery

Further reading

- PDP-11/70 maintenance and installation manual, EK-11070-MM-002

External links

- 11/70 - documentation at Bitsavers

- pdp11 processor handbook - pdp11/04/24/34A/44/70

- PDP-11/70 - contains many good images

- PiDP-11: a functional scale model replica of the PDP-11/70 console

| v • d • e PDP-11 Computers and Peripherals |

|---|

| UNIBUS PDP-11s - PDP-11/20 • PDP-11/15 • PDP-11/35 • PDP-11/40 • PDP-11/45 • PDP-11/50 • PDP-11/55 • PDP-11/70 PDP-11/05 • PDP-11/10 • PDP-11/04 • PDP-11/34 • PDP-11/60 • PDP-11/44 • PDP-11/24 • PDP-11/84 • PDP-11/94 QBUS PDP-11s - PDP-11/03 • PDP-11/23 • PDP-11/23+ • MicroPDP-11/73 • MicroPDP-11/53 • MicroPDP-11/83 • MicroPDP-11/93 QBUS CPUs: LSI-11 • LSI-11/2 • KDF11-A • KDF11-B • KDJ11-A • KDJ11-B • KDJ11-D • KDJ11-E Buses: UNIBUS • UNIBUS map • SPC • MUD • EUB • QBUS • CD interconnect • PMI Also: PDP-11 architecture • PDP-11 Extended Instruction Set • FP11 floating point • PDP-11 Memory Management |

| UNIBUS CPUs: KA11 • KC11 • KB11-A • KB11-B • KB11-C • KB11-D • KD11-A • KD11-B • KD11-D • KD11-E • KD11-EA • KD11-K • KD11-Z • KDF11-U

Co-processors: FP11-A • FP11-B • FP11-C • FP11-E • FP11-F • KE44-A • FPF11 Chips: LSI-11 • KEV11-A • KEV11-B • KEV11-C • F-11 • KEF11-A • KTF11-A • T-11 • J-11 • FPJ11 CPU options: KE11-E • KE11-F • KJ11-A • KT11-C • KT11-D • KK11-A • KK11-B • KT24 • KTJ11-B Rare CPU options: KS11 Memory Protection and Relocation option • KT11-B Paging Option • KUV11 Writeable Control Store Front panels: KY11-A • KY11-D • KY11-J • KY11-LA • KY11-LB • KY11-P More on buses: UNIBUS and QBUS termination • Bus Arbitration on the Unibus and QBUS • CTI BUS PDT-11s - PDT-11/110 • PDT-11/130 • PDT-11/150 CTI PDP-11s - PRO-325 • PRO-350 • PRO-380 Other: FIS floating point • PDP-11 Commercial Instruction Set • PDP-11 stacks • PDP-11 family differences |