Difference between revisions of "KDF11-A CPU"

(Better picture, supported options) |

(+jumpers, details) |

||

| Line 1: | Line 1: | ||

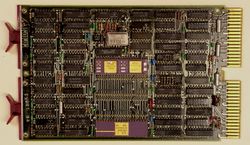

| − | [[Image:KDF11-ATop.jpg|250px|thumb|right| | + | [[Image:KDF11-ATop.jpg|250px|thumb|right| CPU]] |

| − | The '''KDF11-A CPU''' is | + | The '''KDF11-A CPU''' is [[PDP-11]] [[Central Processing Unit|CPU]] for the [[QBUS]]; it is a [[DEC card form factor|dual]]-width [[printed circuit board|card]], the M8186. It uses the same 'Fonz' [[F-11 chip set]] as the other [[KDF11 CPUs]]. |

| − | It contains only the basic CPU, unlike the other KDF-11's: no [[Read-only memory|ROM]], no [[asynchronous serial line]]s, etc. It does support the optional [[KTF11-A memory management chip]] and the [[KEF11-A floating point chip]], but not the [[KEF11-B]] [[PDP-11 Commercial Instruction Set]] (CIS). | + | It contains only the basic CPU, unlike the other KDF-11's: no [[Read-only memory|ROM]], no [[asynchronous serial line]]s, etc. It does support the optional [[KTF11-A memory management chip]] and the [[KEF11-A floating point chip]], but not the [[KEF11-B]] [[PDP-11 Commercial Instruction Set]] (CIS); for higher performance [[floating point]], the [[FPF11 floating point processor]] may be used. |

| − | The first version of the KDF11-A (Revision A) only suppported 256 Kbytes of [[main memory]]; later versions supported up to 4 Mbytes. | + | The first version of the KDF11-A (Revision A) only suppported 256 Kbytes of [[main memory]]; later versions supported up to 4 Mbytes (but their [[QBUS CPU ODT|ODT]]'s are limited to 256 Kbytes). In the later models, a bit in the [[PDP-11 Memory Management#Control|SSR3]] CPU [[register]] must be set to allow use of more than 256 Kbytes. |

| − | {{ | + | ==Configuration== |

| + | |||

| + | A limited amount of configuration can be done with a number of [[jumper]]s in various locations (which differ depending on [[etch]] revision, with block of eleven in the middle of the card.Their functions are: | ||

| + | |||

| + | {| border=1 | ||

| + | ! Jumper !! Function !! In || Out | ||

| + | |- | ||

| + | |W1 || Master Clock || Enabled || Disabled | ||

| + | |- | ||

| + | |W2 || Reserved || Factory || Do not remove | ||

| + | |- | ||

| + | |W3 || Unknown | ||

| + | |- | ||

| + | |W4 || Event line || Disabled || Enabled | ||

| + | |- | ||

| + | |W5 || Powerup option bit 1 | ||

| + | |- | ||

| + | |W6 || Powerup option bit 2 | ||

| + | |- | ||

| + | |W7 || [[Halt]] enable || Halt || [[Trap]] to 4 | ||

| + | |- | ||

| + | |W8 || [[Bootstrap]] [[address]] 0173000 || Yes || W9-W15 | ||

| + | |- | ||

| + | |W09 || Bootstrap address bit 9 || 1 || 0 | ||

| + | |- | ||

| + | |W10 || Bootstrap address bit 10 || 1 || 0 | ||

| + | |- | ||

| + | |W11 || Bootstrap address bit 11 || 1 || 0 | ||

| + | |- | ||

| + | |W12 || Bootstrap address bit 12 || 1 || 0 | ||

| + | |- | ||

| + | |W13 || Bootstrap address bit 13 || 1 || 0 | ||

| + | |- | ||

| + | |W14 || Bootstrap address bit 14 || 1 || 0 | ||

| + | |- | ||

| + | |W15 || Bootstrap address bit 15 || 1 || 0 | ||

| + | |- | ||

| + | |W16 || Reserved || Factory || Do not remove | ||

| + | |- | ||

| + | |W17 || Reserved || Factory || Do not remove | ||

| + | |- | ||

| + | |W18 || Wakeup circuit || Disabled || Enabled | ||

| + | |} | ||

| + | |||

| + | Powerup options are: | ||

| + | |||

| + | {| border=1 | ||

| + | ! W6 !! W5 !! Action | ||

| + | |- | ||

| + | | Out || Out || [[Program Counter|PC]] from 024, [[Processor Status Word|PS]] from 026 | ||

| + | |- | ||

| + | | Out || In || ODT <!--, PS=0 --> | ||

| + | |- | ||

| + | | In || Out || PC=configuration jumpers <!--, PS=340 --> | ||

| + | |- | ||

| + | | In || In || Extended [[microcode]] (trap to 010 if none) | ||

| + | |} | ||

{{PDP-11}} | {{PDP-11}} | ||

Revision as of 13:07, 22 May 2020

The KDF11-A CPU is PDP-11 CPU for the QBUS; it is a dual-width card, the M8186. It uses the same 'Fonz' F-11 chip set as the other KDF11 CPUs.

It contains only the basic CPU, unlike the other KDF-11's: no ROM, no asynchronous serial lines, etc. It does support the optional KTF11-A memory management chip and the KEF11-A floating point chip, but not the KEF11-B PDP-11 Commercial Instruction Set (CIS); for higher performance floating point, the FPF11 floating point processor may be used.

The first version of the KDF11-A (Revision A) only suppported 256 Kbytes of main memory; later versions supported up to 4 Mbytes (but their ODT's are limited to 256 Kbytes). In the later models, a bit in the SSR3 CPU register must be set to allow use of more than 256 Kbytes.

Configuration

A limited amount of configuration can be done with a number of jumpers in various locations (which differ depending on etch revision, with block of eleven in the middle of the card.Their functions are:

| Jumper | Function | In | Out |

|---|---|---|---|

| W1 | Master Clock | Enabled | Disabled |

| W2 | Reserved | Factory | Do not remove |

| W3 | Unknown | ||

| W4 | Event line | Disabled | Enabled |

| W5 | Powerup option bit 1 | ||

| W6 | Powerup option bit 2 | ||

| W7 | Halt enable | Halt | Trap to 4 |

| W8 | Bootstrap address 0173000 | Yes | W9-W15 |

| W09 | Bootstrap address bit 9 | 1 | 0 |

| W10 | Bootstrap address bit 10 | 1 | 0 |

| W11 | Bootstrap address bit 11 | 1 | 0 |

| W12 | Bootstrap address bit 12 | 1 | 0 |

| W13 | Bootstrap address bit 13 | 1 | 0 |

| W14 | Bootstrap address bit 14 | 1 | 0 |

| W15 | Bootstrap address bit 15 | 1 | 0 |

| W16 | Reserved | Factory | Do not remove |

| W17 | Reserved | Factory | Do not remove |

| W18 | Wakeup circuit | Disabled | Enabled |

Powerup options are:

| W6 | W5 | Action |

|---|---|---|

| Out | Out | PC from 024, PS from 026 |

| Out | In | ODT |

| In | Out | PC=configuration jumpers |

| In | In | Extended microcode (trap to 010 if none) |

| v • d • e PDP-11 Computers and Peripherals |

|---|

| UNIBUS PDP-11s - PDP-11/20 • PDP-11/15 • PDP-11/35 • PDP-11/40 • PDP-11/45 • PDP-11/50 • PDP-11/55 • PDP-11/70 PDP-11/05 • PDP-11/10 • PDP-11/04 • PDP-11/34 • PDP-11/60 • PDP-11/44 • PDP-11/24 • PDP-11/84 • PDP-11/94 QBUS PDP-11s - PDP-11/03 • PDP-11/23 • PDP-11/23+ • MicroPDP-11/73 • MicroPDP-11/53 • MicroPDP-11/83 • MicroPDP-11/93 QBUS CPUs: LSI-11 • LSI-11/2 • KDF11-A • KDF11-B • KDJ11-A • KDJ11-B • KDJ11-D • KDJ11-E Buses: UNIBUS • UNIBUS map • SPC • MUD • EUB • QBUS • CD interconnect • PMI Also: PDP-11 architecture • PDP-11 Extended Instruction Set • FP11 floating point • PDP-11 Memory Management |

| UNIBUS CPUs: KA11 • KC11 • KB11-A • KB11-B • KB11-C • KB11-D • KD11-A • KD11-B • KD11-D • KD11-E • KD11-EA • KD11-K • KD11-Z • KDF11-U

Co-processors: FP11-A • FP11-B • FP11-C • FP11-E • FP11-F • KE44-A • FPF11 Chips: LSI-11 • KEV11-A • KEV11-B • KEV11-C • F-11 • KEF11-A • KTF11-A • T-11 • J-11 • FPJ11 CPU options: KE11-E • KE11-F • KJ11-A • KT11-C • KT11-D • KK11-A • KK11-B • KT24 • KTJ11-B Rare CPU options: KS11 Memory Protection and Relocation option • KT11-B Paging Option • KUV11 Writeable Control Store Front panels: KY11-A • KY11-D • KY11-J • KY11-LA • KY11-LB • KY11-P More on buses: UNIBUS and QBUS termination • Bus Arbitration on the Unibus and QBUS • CTI BUS PDT-11s - PDT-11/110 • PDT-11/130 • PDT-11/150 CTI PDP-11s - PRO-325 • PRO-350 • PRO-380 Other: FIS floating point • PDP-11 Commercial Instruction Set • PDP-11 stacks • PDP-11 family differences |