Difference between revisions of "MSV11-M QBUS memory"

(+ reg jumpers) |

m (Jnc moved page MSV11-M memory module to MSV11-M QBUS memory: Actually QBUS mem) |

(No difference)

| |

Revision as of 12:07, 18 October 2020

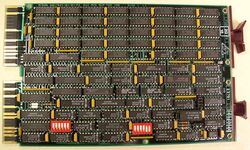

The MSV11-M (M7506) is a dual-height QBUS DRAM main memory card. The MSV11-MB (M7506-BA) holds 1 MByte when fully populated with 256K DRAMs chips, the MSV11-MA (M7506-AA) is half-populated (the only partially-filled configuration allowed) and holds 512 Kbytes.

The memory is arranged as 2 banks, each 16 data bits (1 PDP-11 word) wide, with 2 additional bits for parity (1 per byte). It is a Q22 card; it reportedly supports QBUS block mode.

Configuration

No documentation on the MSV11-M is extant, so it is currently not known how to configure it. The purpose of the two-position jumper between E19 (apparently a delay line) and E18 is currently unknown.

Control Register

Each board has a single control register, which can be configured in the range 17772100-17772136, using the set of four jumpers between chips E27 and E26. They are not numbered on the board; for our purposes we will number them W1-W4, starting with the left-hand jumper, with the board oriented with the insertion handles at the top.

| W4 | W3 | W2 | W1 | CSR Address |

|---|---|---|---|---|

| In | In | In | In | 17772100 |

| In | In | In | Out | 17772102 |

| In | In | Out | In | 17772104 |

| In | In | Out | Out | 17772106 |

| In | Out | In | In | 17772110 |

| In | Out | In | Out | 17772112 |

| In | Out | Out | In | 17772114 |

| In | Out | Out | Out | 17772116 |

| Out | In | In | In | 17772120 |

| Out | In | In | Out | 17772122 |

| Out | In | Out | In | 17772124 |

| Out | In | Out | Out | 17772126 |

| Out | Out | In | In | 17772130 |

| Out | Out | In | Out | 17772132 |

| Out | Out | Out | In | 17772134 |

| Out | Out | Out | Out | 17772136 |

Technical information

As far as is known, there are no copies of the engineering drawings extant for the MSV11-M.

Further reading

- MSV11-M User Guide, EK-MSV1M-UG

- MSV11-M Field Maintenance Printset (MP-02053 - not online)

| v • d • e PDP-11 Computers and Peripherals |

|---|

| UNIBUS PDP-11s - PDP-11/20 • PDP-11/15 • PDP-11/35 • PDP-11/40 • PDP-11/45 • PDP-11/50 • PDP-11/55 • PDP-11/70 PDP-11/05 • PDP-11/10 • PDP-11/04 • PDP-11/34 • PDP-11/60 • PDP-11/44 • PDP-11/24 • PDP-11/84 • PDP-11/94 QBUS PDP-11s - PDP-11/03 • PDP-11/23 • PDP-11/23+ • MicroPDP-11/73 • MicroPDP-11/53 • MicroPDP-11/83 • MicroPDP-11/93 QBUS CPUs: LSI-11 • LSI-11/2 • KDF11-A • KDF11-B • KDJ11-A • KDJ11-B • KDJ11-D • KDJ11-E Buses: UNIBUS • UNIBUS map • SPC • MUD • EUB • QBUS • CD interconnect • PMI Also: PDP-11 architecture • PDP-11 Extended Instruction Set • FP11 floating point • PDP-11 Memory Management |

| UNIBUS CPUs: KA11 • KC11 • KB11-A • KB11-B • KB11-C • KB11-D • KD11-A • KD11-B • KD11-D • KD11-E • KD11-EA • KD11-K • KD11-Z • KDF11-U

Co-processors: FP11-A • FP11-B • FP11-C • FP11-E • FP11-F • KE44-A • FPF11 Chips: LSI-11 • KEV11-A • KEV11-B • KEV11-C • F-11 • KEF11-A • KTF11-A • T-11 • J-11 • FPJ11 CPU options: KE11-E • KE11-F • KJ11-A • KT11-C • KT11-D • KK11-A • KK11-B • KT24 • KTJ11-B Rare CPU options: KS11 Memory Protection and Relocation option • KT11-B Paging Option • KUV11 Writeable Control Store Front panels: KY11-A • KY11-D • KY11-J • KY11-LA • KY11-LB • KY11-P More on buses: UNIBUS and QBUS termination • Bus Arbitration on the Unibus and QBUS • CTI BUS PDT-11s - PDT-11/110 • PDT-11/130 • PDT-11/150 CTI PDP-11s - PRO-325 • PRO-350 • PRO-380 Other: FIS floating point • PDP-11 Commercial Instruction Set • PDP-11 stacks • PDP-11 family differences |