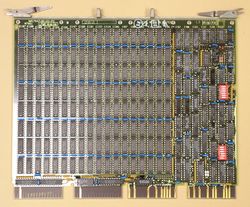

MSV11-Q QBUS memory

The MSV11-Q (M7551) is a quad-height QBUS DRAM main memory card. Initially it used 64Kx1 DRAM chips, later ones use 256Kx1 DRAMs. The memory is arranged as 8 banks, each 16 data bits (1 PDP-11 word) wide, with 2 additional bits for parity (1 per byte).

It holds 1 MByte with 64K DRAMs; 4 Mbytes when fully populated with 256K DRAMs, or 2 Mbytes when half-populated (the only partially-filled configuration allowed). Three versions exist:

- MSV11-QA, 1 Mbyte (64K DRAMs)

- MSV11-QB, 2 Mbytes (256K DRAMs)

- MSV11-QC, 4 Mbytes (256K DRAMs)

all are Q22, and support block mode. The -QA comes in two etch revisions; the latter version supports battery backup. The -QB and -QC are the same etch as the later -QA.

Control Register

Each board has a single control register, which can be configured in the range 172100-172136.

In the register contents (below), all the bits can be read and written by software; most are cleared by power up and bus INIT. Bits which can only be modified by the CPU are shown in normal font, and those which can also be set by the hardware in italics.

| Parity Error | Extended Error Address Enable | Reserved | Error Address | Reserved | Write Wrong Parity | Reserved | Parity Error Enable | ||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

The 'Error Address' field contents depend on the setting of the 'Extended Error Address Enable' bit; when it holds the low address ('Extended Error Address Enable' is 0), it holds address bits 11 through 17; when it holds the high address ('Extended Error Address Enable' is 1), it holds bits 21 through 18 - bits 11-9 of the register are unused.

Technical information

As far as is known, there are no copies of the engineering drawings extant for the MSV11-Q. However, some technical information, enough to repair boards with faulty DRAM chips, has been gathered on it, and that is made available here.

As described above, each board has 8 (sometimes 4) banks in the array of DRAM chips; with 64K chips, each bank is thus 128KB; with 256K chips, they are 512KB. (Note that the MSV11-Q sends a 'write' to all the banks, and selects the one to actually use by use of the RAS signal. It's not certain why DEC did this, but since there is no explicit 'read' signal to the chip, and likely the outputs from all the banks are wire-OR'd together, use of RAS to select the desired bank works for read as well as write.)

The chips in each bank run across the board (when it is oriented with the chip side facing the viewer, with the metal edging holding the handles at the top). Bit 0 (value 1) is on the left hand edge of the array; bit 15 (value 0100000) is on the right, with the two parity bits in the middle. The banks run down the board from the metal handle edge; bank 0 is next to the handles, and bank 7 is down near the contact fingers.

Thus, for example, bit 0 of bank 0 is in chip E197. The full table is:

| Bit | Bank 0 | Bank 1 | Bank 2 | Bank 3 | Bank 4 | Bank 5 | Bank 6 | Bank 7 |

|---|---|---|---|---|---|---|---|---|

| 01 | E197 | E196 | E195 | E194 | E193 | E192 | E191 | E190 |

| 02 | E189 | E188 | E187 | E186 | E185 | E184 | E183 | E182 |

| 04 | E180 | E179 | E178 | E177 | E176 | E175 | E174 | E173 |

| 10 | E172 | E171 | E170 | E170 | E169 | E168 | E167 | E166 |

| 20 | E164 | E163 | E162 | E161 | E160 | E159 | E158 | E157 |

| 40 | E155 | E154 | E153 | E152 | E151 | E150 | E149 | E148 |

| 100 | E147 | E146 | E145 | E144 | E143 | E142 | E141 | E140 |

| 200 | E139 | E138 | E137 | E136 | E135 | E134 | E133 | E132 |

| 400 | E114 | E113 | E112 | E111 | E110 | E109 | E108 | E107 |

| 1000 | E105 | E104 | E103 | E102 | E101 | E100 | E99 | E98 |

| 2000 | E97 | E96 | E95 | E94 | E93 | E92 | E91 | E90 |

| 4000 | E89 | E88 | E87 | E86 | E85 | E84 | E83 | E82 |

| 10000 | E81 | E80 | E79 | E78 | E77 | E76 | E75 | E74 |

| 20000 | E72 | E71 | E70 | E70 | E69 | E68 | E67 | E66 |

| 40000 | E64 | E63 | E62 | E61 | E60 | E59 | E58 | E57 |

| 100000 | E56 | E55 | E54 | E53 | E52 | E51 | E50 | E49 |

The following 64K DRAM chips have been observed to be used: M5K4164ANP-15P (Micron Technologies), NEC D4164C211 (NEC Electronics).

Further reading

- MSV11-Q MOS Memory User's Guide (EK-MSV1Q-UG-002)

- Microcomputer Products Handbook (1985), Chapter 15

- MSV11-QA, MSV11-QB, and MSV11-QC Field Maintenance Printset (MP-01931 - not online)

| v • d • e PDP-11 Computers and Peripherals |

|---|

| UNIBUS PDP-11s - PDP-11/20 • PDP-11/15 • PDP-11/35 • PDP-11/40 • PDP-11/45 • PDP-11/50 • PDP-11/55 • PDP-11/70 PDP-11/05 • PDP-11/10 • PDP-11/04 • PDP-11/34 • PDP-11/60 • PDP-11/44 • PDP-11/24 • PDP-11/84 • PDP-11/94 QBUS PDP-11s - PDP-11/03 • PDP-11/23 • PDP-11/23+ • MicroPDP-11/73 • MicroPDP-11/53 • MicroPDP-11/83 • MicroPDP-11/93 QBUS CPUs: LSI-11 • LSI-11/2 • KDF11-A • KDF11-B • KDJ11-A • KDJ11-B • KDJ11-D • KDJ11-E Buses: UNIBUS • UNIBUS map • SPC • MUD • EUB • QBUS • CD interconnect • PMI Also: PDP-11 architecture • PDP-11 Extended Instruction Set • FP11 floating point • PDP-11 Memory Management |

| UNIBUS CPUs: KA11 • KC11 • KB11-A • KB11-B • KB11-C • KB11-D • KD11-A • KD11-B • KD11-D • KD11-E • KD11-EA • KD11-K • KD11-Z • KDF11-U

Co-processors: FP11-A • FP11-B • FP11-C • FP11-E • FP11-F • KE44-A • FPF11 Chips: LSI-11 • KEV11-A • KEV11-B • KEV11-C • F-11 • KEF11-A • KTF11-A • T-11 • J-11 • FPJ11 CPU options: KE11-E • KE11-F • KJ11-A • KT11-C • KT11-D • KK11-A • KK11-B • KT24 • KTJ11-B Rare CPU options: KS11 Memory Protection and Relocation option • KT11-B Paging Option • KUV11 Writeable Control Store Front panels: KY11-A • KY11-D • KY11-J • KY11-LA • KY11-LB • KY11-P More on buses: UNIBUS and QBUS termination • Bus Arbitration on the Unibus and QBUS • CTI BUS PDT-11s - PDT-11/110 • PDT-11/130 • PDT-11/150 CTI PDP-11s - PRO-325 • PRO-350 • PRO-380 Other: FIS floating point • PDP-11 Commercial Instruction Set • PDP-11 stacks • PDP-11 family differences |