Difference between revisions of "PDP-11/05"

(→Control PROMs: Add chip functions for etch rev E control board) |

(→Control PROMs: Add control board etch rev F functions) |

||

| Line 189: | Line 189: | ||

{| class="wikitable" | {| class="wikitable" | ||

| − | ! Part Number !! Package !! Type | + | ! Part Number !! Package !! Type !! Function |

|- | |- | ||

| − | | A01A2 || E24* || 256x4 | + | | A01A2 || E24* || 256x4 || Bus Request -> Grant processing |

|- | |- | ||

| − | | A02A2 || E53* || 256x4 | + | | A02A2 || E53* || 256x4 || Internal address decode (first stage) |

|- | |- | ||

| − | | A04A2 || E102* || 256x4 | + | | A04A2 || E102* || 256x4 || Microprogram - Next instruction (high bits) |

|- | |- | ||

| − | | A05A2 || E104* || 256x4 | + | | A05A2 || E104* || 256x4 || Microprogram - Processor Status Word control |

|- | |- | ||

| − | | A07A1 || E71* || 32x8 | + | | A07A1 || E71* || 32x8 || Internal address decode (second stage) |

|- | |- | ||

| − | | A09A1 || E72* || 32x8 | + | | A09A1 || E72* || 32x8 || Internal address decode (second stage) |

|- | |- | ||

| − | | A09A2 || E107* || 256x4 | + | | A09A2 || E107* || 256x4 || Branch utest service |

|- | |- | ||

| − | | A10A2 || E112* || 256x4 | + | | A10A2 || E112* || 256x4 || Microprogram - Next instruction (low bits) |

|- | |- | ||

| − | | A11A2 || E114* || 256x4 | + | | A11A2 || E114* || 256x4 || Microprogram - ALU operation select |

|- | |- | ||

| − | | A13A2 || E115* || 256x4 | + | | A13A2 || E115* || 256x4 || Microprogram - Multiplexor control |

|- | |- | ||

| − | | A14A1* || E108 || 32x8 | + | | A14A1* || E108 || 32x8 || Console switch control |

|- | |- | ||

| − | | A16A2 || E105* || 256x4 | + | | A16A2 || E105* || 256x4 || Microprogram - Miscellaneous |

|- | |- | ||

| − | | A17A2 || E106* || 256x4 | + | | A17A2 || E106* || 256x4 || Microprogram - Bus control |

|- | |- | ||

| − | | A18A2* || E113 || 256x4 | + | | A18A2* || E113 || 256x4 || Microprogram - Branch utest |

|- | |- | ||

| − | | A19A2* || E116 || 256x4 | + | | A19A2* || E116 || 256x4 || Microprogram - Bus control |

|- | |- | ||

| − | | A20A2* || E103 || 256x4 | + | | A20A2* || E103 || 256x4 || Microprogram - ALU control |

|} | |} | ||

| − | Note that the 'F' etch revision has one less PROM than the 'E' revision, but it | + | Note that the 'F' etch revision has one less PROM than the 'E' revision, but it is not a micro-program PROM - the 'missing' chip is a 32x8 PROM used for internal interrupt functions; it was replaced by a 74154 4->16 demultiplexor (E110). |

==Prints== | ==Prints== | ||

Revision as of 16:12, 7 May 2016

| PDP-11/05 | |

| Manufacturer: | Digital Equipment Corporation |

|---|---|

| Architecture: | PDP-11 |

| Year Introduced: | June 1972 |

| Word Size: | 16 bit |

| Physical Address Size: | 18 bit (only 16 bits usable) |

| Bus Architecture: | UNIBUS |

The PDP-11/05 was the fourth processor in the PDP-11 series, following the PDP-11/20, the PDP-11/45 and the PDP-11/40; it used the KD11-B CPU. It was intended as a cost-reduced low-end machine to replace the PDP-11/20. Like all the other early PDP-11's, it was a UNIBUS machine.

The PDP-11/05 was identical to the PDP-11/10; the only difference between the /05 and the /10 was the number on the front panel. The /05 was aimed toward the OEM market, while the /10 was intended for end-users. General usage (following DEC's lead) is to refer to all these machines as '11/05s'.

The KD11-B was a two-board micro-programmed processor contained on two hex cards.

Backplane versions

The PDP-11/05 and /10 came in three versions, with different main backplanes (the 9-slot unit holding the two CPU cards).

The original /05 and /10 came with backplanes wired to hold MM11-L 16 Kbyte core memory units. There were two different backplanes: one held two memory units, with one slot left for SPC devices; the other held one memory unit, and provided four SPC slots.

A second version, the /05N and /10N, came in a 10-1/2 inch box and had a slightly different backplane, which had space for two MM11-L memory units, but deleted the SPC slot of the previous double MM11-L backplane, and replaced it with a slot to hold the dual-height M9970 console terminal cable board.

The later /05S and /10S came with a backplane wired to hold an MM11-U 32 Kbyte core memory, and which provided three SPC slots.

CPU board versions

The two boards in the PDP-11/05-10 (the M7260 data paths module, and the M7261 control logic module) both come in two markedly-different versions, but unlike later practise (as in, e.g. the PDP-11/34), the two versions are not given different M-numbers, or clearly marked with a revision (i.e. 'M7260' and 'M7260-AA') on the handles.

One easy way to visually distinguish the early M7260 from later ones is that the later ones contain a circular selector switch in the upper left corner to select the baud rate of the built-in serial line; also, the position of the large UART chip has a different location (from down near the contact fingers, to up near the handles) and orientation (parellel to the board's long axis, in the earlier revision). For the M7261, the early version of the board has a large blank area, containing only traces, in the left middle area of the board.

The early revision of the M7260 is the 'B' revision; the later is the 'C' revision (the latter is marked as such, on the back side of the board- "M7260C"). For the M7261, two early revisions are the 'C' and 'E' revisions (the latter also similarly marked - "M7261E"); the later is the 'F' (also marked).

The early version of the M7260 only supports 110 baud operation; the latter has a circular selector switch which allows operation at a range of speeds from 110 baud up to 2400 baud; however, it is necessary to tweak a trim pot to change from the 110/220/440/880/1760 speed set to the 150/300/600/1200/2400 set.

The later revision of the M7261 contains two jumpers which are not present on the earlier revision. One (W1) disables to built-in serial line (which is 20mA, and limited to 2400 baud), allowing use of a more capable serial interface as the system console. The other (W2) disables the CPU from acting as a bus arbitrator, so that the machine can be a 'slave' processor, on a UNIBUS controlled by another CPU.

Control PROMs

The KD11-B makes extensive use of PROMs in place of random logic for control purposes; both boards contain a large number of PROMs. The two types used are IM5600 (or equivalent) 32x8 PROM, the IM5603 256x4 PROM (on the M7261), and the 74187 256x4 PROM (on the M7260).

On the early version (etch revision B) of the M7260 Data Paths board:

| Part Number | Package | Type |

|---|---|---|

| A01A1 | E25 | 32x8 |

| A02A1 | E53 | 32x8 |

| A03A1 | E61 | 32x8 |

| A03A2 | E59 | 256x4 |

| A04A1 | E64 | 32x8 |

| A05A1 | E66 | 32x8 |

| A06A1 | E68 | 32x8 |

| A08A1 | E69 | 32x8 |

| A10A1 | E71 | 32x8 |

| A11A1 | E74 | 32x8 |

| A12A1 | E82 | 32x8 |

On the later version (etch revision C) of the M7260 Data Paths board (apparently all the same parts, but mostly in different locations; differing locations are marked with a '*'):

| Part Number | Package | Type |

|---|---|---|

| A01A1 | E44* | 32x8 |

| A02A1 | E53 | 32x8 |

| A03A1 | E54* | 32x8 |

| A03A2 | E72* | 256x4 |

| A04A1 | E65* | 32x8 |

| A05A1 | E59* | 32x8 |

| A06A1 | E66* | 32x8 |

| A08A1 | E78* | 32x8 |

| A10A1 | E77* | 32x8 |

| A11A1 | E83* | 32x8 |

| A12A1 | E69* | 32x8 |

On the early version (C etch revision) of the M7261 Control Logic and Microprogram board (differences with the next revision marked with a '*'):

| Part Number | Package | Type | Function |

|---|---|---|---|

| A01A2 | E12 | 256x4 | Bus Request -> Grant processing |

| A02A2 | E30 | 256x4 | Internal address decode (first stage) |

| A04A2 | E92 | 256x4 | Microprogram - Next instruction (high bits) |

| A05A2 | E93 | 256x4 | Microprogram - Processor Status Word control |

| A07A1 | E68 | 32x8 | Internal address decode (second stage) |

| A07A2* | E95 | 256x4 | Microprogram - Bus control |

| A09A1 | E69 | 32x8 | Internal address decode (second stage) |

| A09A2 | E101 | 256x4 | Branch utest service |

| A10A2 | E103 | 256x4 | Microprogram - Next instruction (low bits) |

| A11A2 | E104 | 256x4 | Microprogram - ALU operation select |

| A12A2 | E105 | 256x4 | Microprogram - Branch utest |

| A13A1 | E90 | 32x8 | Internal interrupt acknowledge |

| A13A2 | E106 | 256x4 | Microprogram - Multiplexor control |

| A14A1* | E100 | 32x8 | Console switch control |

| A14A2 | E107 | 256x4 | Microprogram - Bus control |

| A15A2 | E94 | 256x4 | Microprogram - ALU control |

| A16A2 | E96 | 256x4 | Microprogram - Miscellaneous |

It appears that on an earlier revision of the prints, the chip in E96 (A16A2 in this revision) was actually a different version, A8A2; the prints show the later one in the parts list, but the earlier one in the actual drawing.

On another early version (E etch revision) of the M7261 Control Logic and Microprogram board (differences with the earlier revision are marked with a '+', differences with the later revision below are marked with a '-'):

| Part Number | Package | Type | Function |

|---|---|---|---|

| A01A2 | E12 | 256x4 | Bus Request -> Grant processing |

| A02A2 | E30 | 256x4 | Internal address decode (first stage) |

| A04A2 | E92 | 256x4 | Microprogram - Next instruction (high bits) |

| A05A2 | E93 | 256x4 | Microprogram - Processor Status Word control |

| A07A1 | E68 | 32x8 | Internal address decode (second stage) |

| A09A1 | E69 | 32x8 | Internal address decode (second stage) |

| A09A2 | E101 | 256x4 | Branch utest service |

| A10A2 | E103 | 256x4 | Microprogram - Next instruction (low bits) |

| A11A2 | E104 | 256x4 | Microprogram - ALU operation select |

| A12A2- | E105 | 256x4 | Microprogram - Branch utest |

| A13A1- | E90 | 32x8 | Internal interrupt acknowledge |

| A13A2 | E106 | 256x4 | Microprogram - Multiplexor control |

| A14A2- | E107 | 256x4 | Microprogram - Bus control |

| A15A2- | E94 | 256x4 | Microprogram - ALU control |

| A16A1+- | E100 | 32x8 | Console switch control |

| A16A2 | E96 | 256x4 | Microprogram - Miscellaneous |

| A17A2+ | E95 | 256x4 | Microprogram - Bus control |

(The actual drawing shows an A14A1 at location E100, not an A16A1, but the later one is in the parts list.)

On the later version (F etch revision) of the M7261 Control Logic and Microprogram board (apparently mostly the same parts as the previous revision, but all in different locations; differences in type and location with the earlier revision are marked with a '*' in the appropriate column):

| Part Number | Package | Type | Function |

|---|---|---|---|

| A01A2 | E24* | 256x4 | Bus Request -> Grant processing |

| A02A2 | E53* | 256x4 | Internal address decode (first stage) |

| A04A2 | E102* | 256x4 | Microprogram - Next instruction (high bits) |

| A05A2 | E104* | 256x4 | Microprogram - Processor Status Word control |

| A07A1 | E71* | 32x8 | Internal address decode (second stage) |

| A09A1 | E72* | 32x8 | Internal address decode (second stage) |

| A09A2 | E107* | 256x4 | Branch utest service |

| A10A2 | E112* | 256x4 | Microprogram - Next instruction (low bits) |

| A11A2 | E114* | 256x4 | Microprogram - ALU operation select |

| A13A2 | E115* | 256x4 | Microprogram - Multiplexor control |

| A14A1* | E108 | 32x8 | Console switch control |

| A16A2 | E105* | 256x4 | Microprogram - Miscellaneous |

| A17A2 | E106* | 256x4 | Microprogram - Bus control |

| A18A2* | E113 | 256x4 | Microprogram - Branch utest |

| A19A2* | E116 | 256x4 | Microprogram - Bus control |

| A20A2* | E103 | 256x4 | Microprogram - ALU control |

Note that the 'F' etch revision has one less PROM than the 'E' revision, but it is not a micro-program PROM - the 'missing' chip is a 32x8 PROM used for internal interrupt functions; it was replaced by a 74154 4->16 demultiplexor (E110).

Prints

Prints for both major versions of the CPU cards are available online; the earlier ones may be found in the GT40 Engineering Drawings set dated February, 1973 (pp. 141-150 for the M7260, and pp. 162-173 for the M7261).

The following table contains details of exactly which board etch revisions are covered in which sets of prints, for both boards:

| Drawing Set | Date | M7260 | M7261 |

|---|---|---|---|

| PDP-11/05 Engineering Drawings, Revision B (not online yet) | May, 1972 | B | C |

| GT40 Engineering Drawings | February, 1973 | B | E |

| PDP-11/05S System Engineering Drawings, Revision D | October, 1974 | C | F |

| PDP-11/05 Engineering Drawings, Revision AH | July, 1976 | C | F |

Keys

Unlike all the other PDP-11s, which use a circular Ace key, the /05's (and /10s) use a normal flat Yale-type key. The original key is a Chicago Lock Company key, code "GRB 2"; this is cut 215, on a Chicago K5K or Ilco S1041T blank. If simply duplicating an existing key, Hillman Y11 and FR4 blanks may be used (both work, but one has to be trimmed a bit, length-wise).

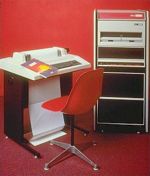

Gallery

| v • d • e PDP-11 Computers and Peripherals |

|---|

| UNIBUS PDP-11s - PDP-11/20 • PDP-11/15 • PDP-11/35 • PDP-11/40 • PDP-11/45 • PDP-11/50 • PDP-11/55 • PDP-11/70 PDP-11/05 • PDP-11/10 • PDP-11/04 • PDP-11/34 • PDP-11/60 • PDP-11/44 • PDP-11/24 • PDP-11/84 • PDP-11/94 QBUS PDP-11s - PDP-11/03 • PDP-11/23 • PDP-11/23+ • MicroPDP-11/73 • MicroPDP-11/53 • MicroPDP-11/83 • MicroPDP-11/93 QBUS CPUs: LSI-11 • LSI-11/2 • KDF11-A • KDF11-B • KDJ11-A • KDJ11-B • KDJ11-D • KDJ11-E Buses: UNIBUS • UNIBUS map • SPC • MUD • EUB • QBUS • CD interconnect • PMI Also: PDP-11 architecture • PDP-11 Extended Instruction Set • FP11 floating point • PDP-11 Memory Management |

| UNIBUS CPUs: KA11 • KC11 • KB11-A • KB11-B • KB11-C • KB11-D • KD11-A • KD11-B • KD11-D • KD11-E • KD11-EA • KD11-K • KD11-Z • KDF11-U

Co-processors: FP11-A • FP11-B • FP11-C • FP11-E • FP11-F • KE44-A • FPF11 Chips: LSI-11 • KEV11-A • KEV11-B • KEV11-C • F-11 • KEF11-A • KTF11-A • T-11 • J-11 • FPJ11 CPU options: KE11-E • KE11-F • KJ11-A • KT11-C • KT11-D • KK11-A • KK11-B • KT24 • KTJ11-B Rare CPU options: KS11 Memory Protection and Relocation option • KT11-B Paging Option • KUV11 Writeable Control Store Front panels: KY11-A • KY11-D • KY11-J • KY11-LA • KY11-LB • KY11-P More on buses: UNIBUS and QBUS termination • Bus Arbitration on the Unibus and QBUS • CTI BUS PDT-11s - PDT-11/110 • PDT-11/130 • PDT-11/150 CTI PDP-11s - PRO-325 • PRO-350 • PRO-380 Other: FIS floating point • PDP-11 Commercial Instruction Set • PDP-11 stacks • PDP-11 family differences |