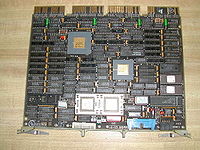

KDJ11-B CPU

The KDJ11-B CPU board (M8190) is the second-generation QBUS CPU card using the J-11 chip of the PDP-11 (the first being the the KDJ11-A, used in the PDP-11/73).

Its principal improvement over the KDJ11-A is its support of the Private Memory Interconnect bus, a high-performance variant of the QBUS; it also supports the [[KTJ11

The KDJ11-B CPU board (M8190) is the second-generation QBUS CPU card using the J-11 chip of the PDP-11 (the first being the the KDJ11-A, used in the PDP-11/73); it is a quad-height board.

Its principal improvement over the KDJ11-A is its support of the Private Memory Interconnect bus, a high-performance variant of the QBUS; it also supports the KTJ11-B, a QBUS->UNIBUS adaptor.

It also provides a built-in serial console, and ROMs to contain diagnostic and boot programs, and an EEPROM to contain configuration information.

Like the KDJ11-A, the -B also contains an 8K-byte write-through cache (set size 1, block size 1 16-bit word), protected by parity; the KDJ11-B provides two sets of tag fields for each cache entry, however, so that the CPU and DMA can interact with the cache simultaneously. Again, cache control logic inspects DMA transfers and invalidates cache entries for memory which is written to by a device.

Also like the KDJ11-A, it can also use the FPJ11 Floating Point Accelerator to speed up the FP11 implementation in the J-11.

| v • d • e PDP-11 Computers and Peripherals |

|---|

| UNIBUS PDP-11s - PDP-11/20 • PDP-11/15 • PDP-11/35 • PDP-11/40 • PDP-11/45 • PDP-11/50 • PDP-11/55 • PDP-11/70 PDP-11/05 • PDP-11/10 • PDP-11/04 • PDP-11/34 • PDP-11/60 • PDP-11/44 • PDP-11/24 • PDP-11/84 • PDP-11/94 QBUS PDP-11s - PDP-11/03 • PDP-11/23 • PDP-11/23+ • MicroPDP-11/73 • MicroPDP-11/53 • MicroPDP-11/83 • MicroPDP-11/93 QBUS CPUs: LSI-11 • LSI-11/2 • KDF11-A • KDF11-B • KDJ11-A • KDJ11-B • KDJ11-D • KDJ11-E Buses: UNIBUS • UNIBUS map • SPC • MUD • EUB • QBUS • CD interconnect • PMI Also: PDP-11 architecture • PDP-11 Extended Instruction Set • FP11 floating point • PDP-11 Memory Management |

| UNIBUS CPUs: KA11 • KC11 • KB11-A • KB11-B • KB11-C • KB11-D • KD11-A • KD11-B • KD11-D • KD11-E • KD11-EA • KD11-K • KD11-Z • KDF11-U

Co-processors: FP11-A • FP11-B • FP11-C • FP11-E • FP11-F • KE44-A • FPF11 Chips: LSI-11 • KEV11-A • KEV11-B • KEV11-C • F-11 • KEF11-A • KTF11-A • T-11 • J-11 • FPJ11 CPU options: KE11-E • KE11-F • KJ11-A • KT11-C • KT11-D • KK11-A • KK11-B • KT24 • KTJ11-B Rare CPU options: KS11 Memory Protection and Relocation option • KT11-B Paging Option • KUV11 Writeable Control Store Front panels: KY11-A • KY11-D • KY11-J • KY11-LA • KY11-LB • KY11-P More on buses: UNIBUS and QBUS termination • Bus Arbitration on the Unibus and QBUS • CTI BUS PDT-11s - PDT-11/110 • PDT-11/130 • PDT-11/150 CTI PDP-11s - PRO-325 • PRO-350 • PRO-380 Other: FIS floating point • PDP-11 Commercial Instruction Set • PDP-11 stacks • PDP-11 family differences |